NB7L14M

Overview

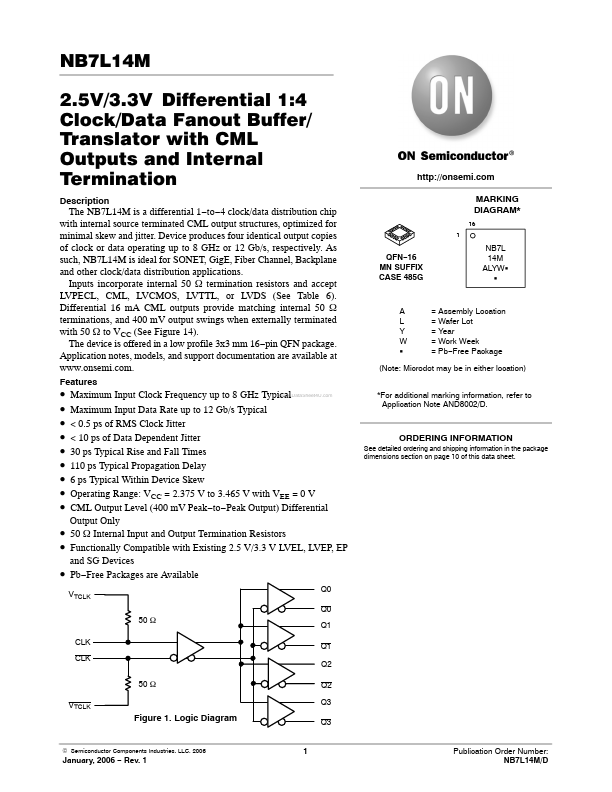

- Maximum Input Clock Frequency up to 8 GHz Typical Maximum Input Data Rate up to 12 Gb/s Typical < 0.5 ps of RMS Clock Jitter < 10 ps of Data Dependent Jitter 30 ps Typical Rise and Fall Times 110 ps Typical Propagation Delay 6 ps Typical Within Device Skew Operating Range: VCC = 2.375 V to 3.465 V with VEE = 0 V CML Output Level (400 mV Peak-to-Peak Output) Differential Output Only 50 W Internal Input and Output Termination Resistors Functionally Compatible with Existing 2.5 V/3.3 V LVEL, LVEP, EP and SG Devices Pb-Free Packages are Available