NIS1050

NIS1050 is Protection Interface manufactured by onsemi.

Features

- Lower Power Dissipation and Higher Efficiency vs. Zener Shunt

Regulator

- LDO Highly Stable across Temperature, Operates Without Bypass

Capacitors

- Wide 3-30 V Power Supply Voltage Input Range

- Low- Profile (0.75mm) 6-Lead 2x2mm WDFN6 Package

- This is a Pb- Free Device

Typical Applications

- Power Interface for New Generation PMICs from Leading Mobile

Phone and UMPC Chipset Vendors http://onsemi.

MARKING DIAGRAMS

WDFN6, 2x2 CASE 506AN

1 PM M

PM = Specific Device Code M = Date Code

ORDERING INFORMATION

Device

Package

Shipping†

NIS1050MNTBG WDFN6 3000 / Tape & Reel (Pb- Free)

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

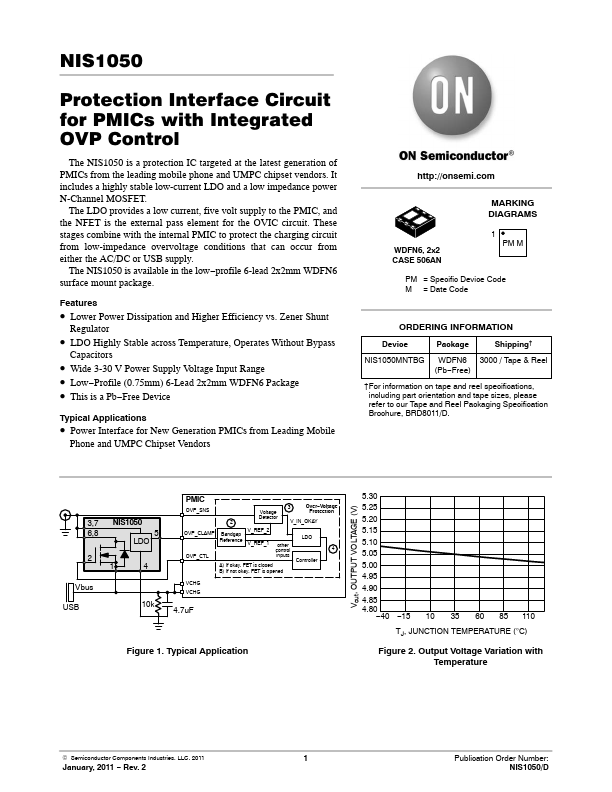

3,7 NIS1050

6,8

Vbus

10k

PMIC

OVP_SNS

OVP_CLAMP

OVP_CTL

3 Voltage

Over- Voltage Protection

Detector

V_IN_OKAY

V_REF_2

Bandgap Reference

V_REF_1 other...