NL17SHT08

Features

- High Speed: t PD = 3.5 ns (Typ) at VCC = 5 V

- Low Power Dissipation: ICC = 1 m A (Max) at TA = 25°C

- TTL- patible Inputs: VIL = 0.8 V; VIH = 2 V

- CMOS- patible Outputs: VOH > 0.8 VCC; VOL < 0.1 VCC @Load

- Power Down Protection Provided on Inputs and Outputs

- Balanced Propagation Delays

- Pin and Function patible with Other Standard Logic Families

- These are Pb- Free Devices

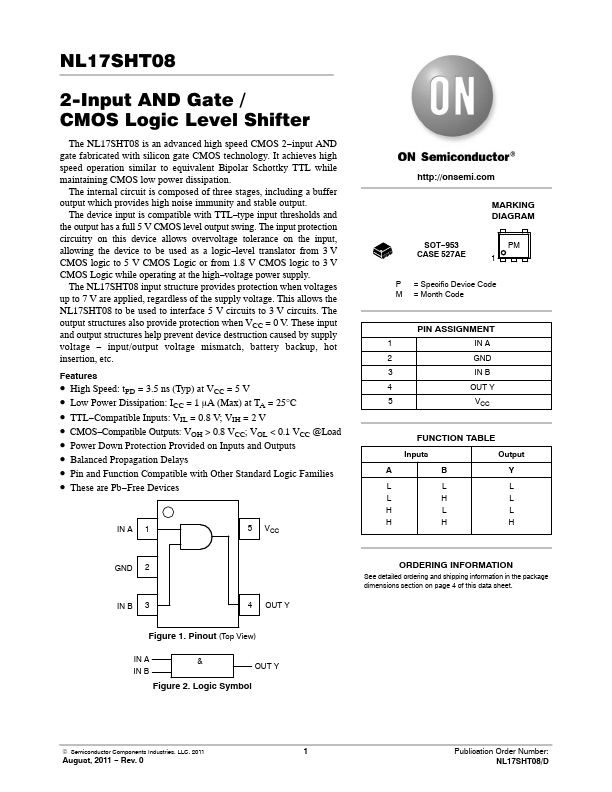

IN A 1

5 VCC http://onsemi.

MARKING DIAGRAM

SOT- 953 CASE 527AE

PM 1

P = Specific Device Code M = Month Code

PIN ASSIGNMENT

IN A

IN B

OUT Y

FUNCTION TABLE

Inputs

Output...