| Part | NSBC114EPDXV6T1 |

|---|---|

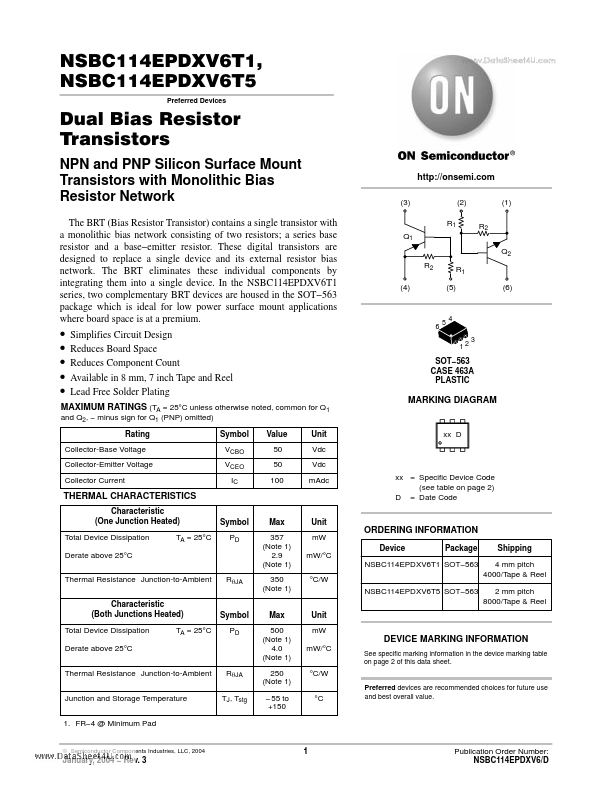

| Description | Dual Bias Resistor Transistors |

| Category | Transistor |

| Manufacturer | onsemi |

| Size | 205.90 KB |

Pricing from 0.0453 USD, available from Verical and Master Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Verical | 3700 | 127+ : 0.0453 USD | View Offer |

| Verical | 3500 | 3500+ : 0.0659 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| BD777 | Motorola Semiconductor | Plastic Darlington Complementary Silicon Power Transistors |

| D718 | SavantIC | Silicon NPN Power Transistors |

| C33725 | onsemi | Amplifier Transistors |