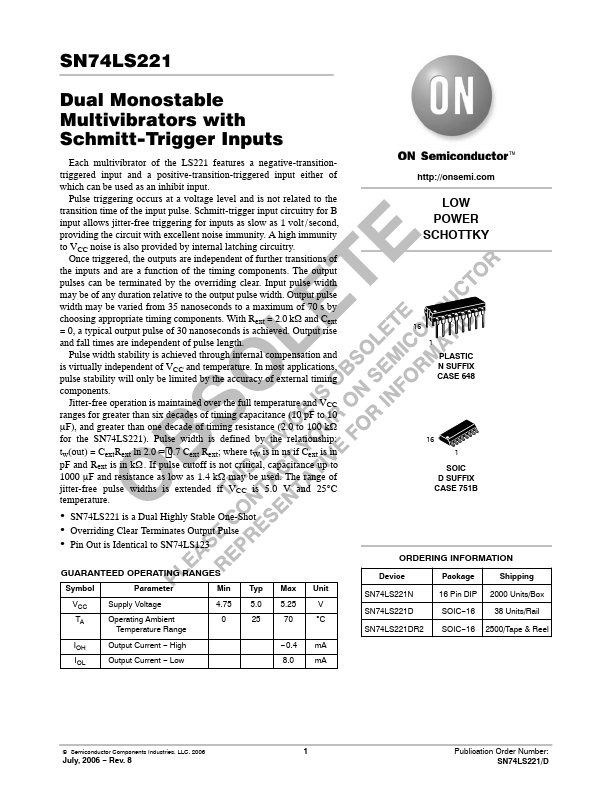

74LS221 Overview

Key Features

- a negative-transitiontriggered input and a positive-transition-triggered input either of which can be used as an inhibit input

- Pulse triggering occurs at a voltage level and is not related to the transition time of the input pulse

- A high immunity to VCC noise is also provided by internal latching circuitry

- Once triggered, the outputs are independent of further transitions of the inputs and are a function of the timing components

- The output pulses can be terminated by the overriding clear

- Input pulse width may be of any duration relative to the output pulse width

- Output pulse width may be varied from 35 nanoseconds to a maximum of 70 s by choosing appropriate timing components

- With Rext = 2.0 kΩ and Cext = 0, a typical output pulse of 30 nanoseconds is achieved

- Output rise and fall times are independent of pulse length

- Pulse width stability is achieved through internal compensation and is virtually independent of VCC and temperature