82C621A

Overview

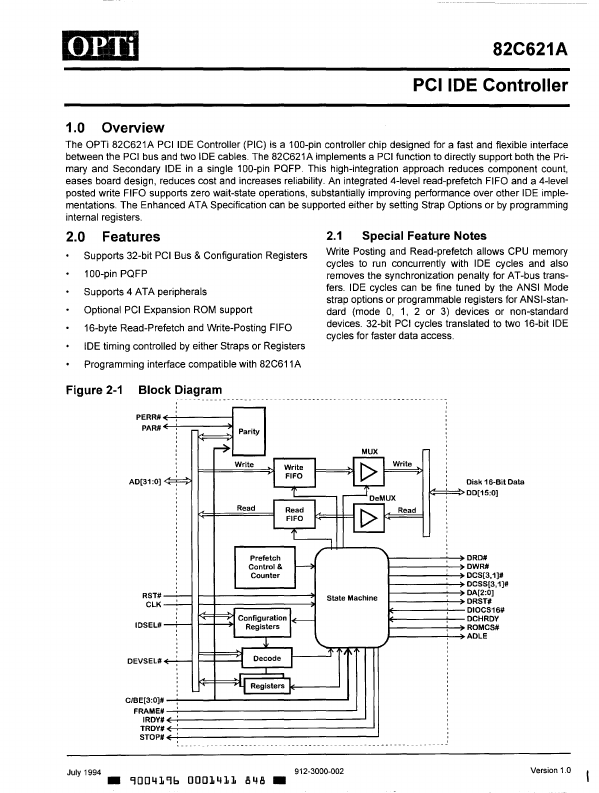

- 1 Special Feature Notes Write Posting and Read-prefetch allows CPU memory cycles to run concurrently with IDE cycles and also removes the synchronization penalty for AT-bus transfers. IDE cycles can be fine tuned by the ANSI Mode strap options or programmable registers for ANSI-standard (mode 0, 1, 2 or 3) devices or non-standard devices. 32-bit PCI cycles translated to two 16-bit IDE cycles for faster data access. Programming interface compatible with 82C611A