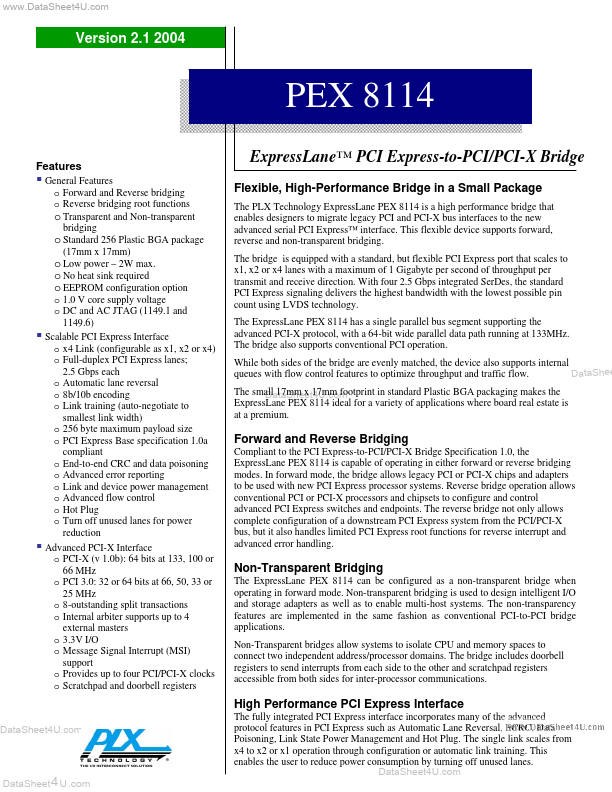

PEX8114

PEX8114 is PCI Express to PCI Bridge manufactured by PLX Technology.

Features

Express Lane™ PCI Express-to-PCI/PCI-X Bridge

Flexible, High-Performance Bridge in a Small Package

The PLX Technology Express Lane PEX 8114 is a high performance bridge that enables designers to migrate legacy PCI and PCI-X bus interfaces to the new advanced serial PCI Express™ interface. This flexible device supports forward, reverse and non-transparent bridging. The bridge is equipped with a standard, but flexible PCI Express port that scales to x1, x2 or x4 lanes with a maximum of 1 Gigabyte per second of throughput per transmit and receive direction. With four 2.5 Gbps integrated Ser Des, the standard PCI Express signaling delivers the highest bandwidth with the lowest possible pin count using LVDS technology. The Express Lane PEX 8114 has a single parallel bus segment supporting the advanced PCI-X protocol, with a 64-bit wide parallel data path running at 133MHz. The bridge also supports conventional PCI operation.

- General Features o Forward and Reverse bridging o Reverse bridging root functions o Transparent and Non-transparent bridging o Standard 256 Plastic BGA package (17mm x 17mm) o Low power

- 2W max. o No heat sink required o EEPROM configuration option o 1.0 V core supply voltage o DC and AC JTAG (1149.1 and 1149.6)

- Scalable PCI Express Interface o x4 Link (configurable as x1, x2 or x4) o Full-duplex PCI Express lanes; 2.5 Gbps each o Automatic lane reversal o 8b/10b encoding o Link training (auto-negotiate to smallest link width) o 256 byte maximum payload size o PCI Express Base specification 1.0a pliant o End-to-end CRC and data poisoning o Advanced error reporting o Link and device power management o Advanced flow control o Hot Plug o Turn off unused lanes for power reduction

- Advanced PCI-X Interface o PCI-X (v 1.0b): 64 bits at 133, 100 or 66 MHz o PCI 3.0: 32 or 64 bits at 66, 50, 33 or 25 MHz o 8-outstanding split transactions o Internal arbiter supports up to 4 external masters o 3.3V I/O o Message Signal Interrupt (MSI) support o...