PM7389 Overview

Key Specifications

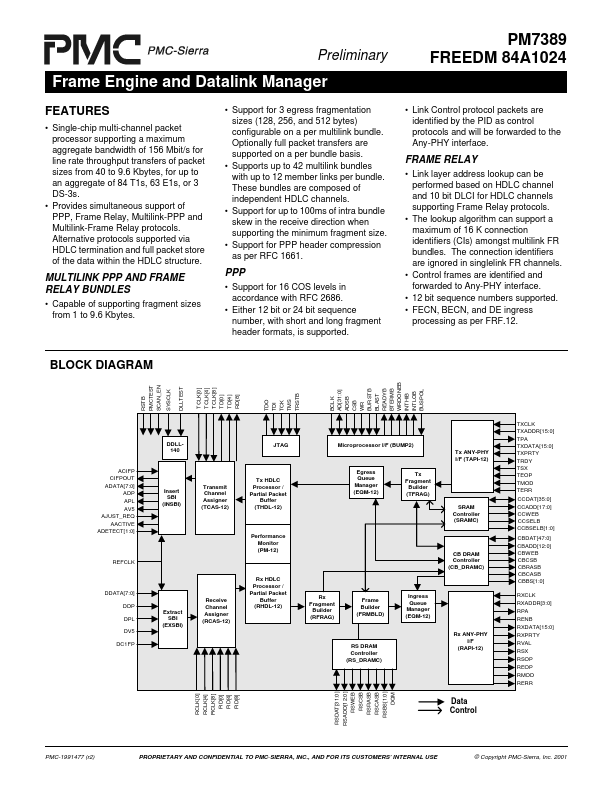

Key Features

- Supports up to 42 multilink bundles with up to 12 member links per bundle. These bundles are composed of independent HDLC channels

- Support for up to 100ms of intra bundle skew in the receive direction when supporting the minimum fragment size

- Support for PPP header compression as per RFC

- Link Control protocol packets are identified by the PID as control protocols and will be forwarded to the Any-PHY interface. FRAME RELAY

- Link layer address lookup can be performed based on HDLC channel and 10 bit DLCI for HDLC channels supporting Frame Relay protocols