PM8351 Overview

Key Specifications

Key Features

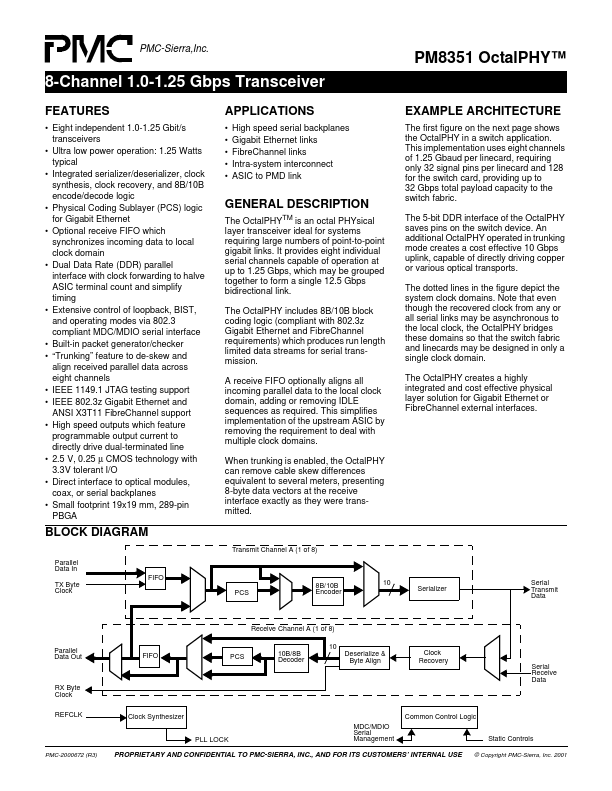

- Eight independent 1.0-1.25 Gbit/s transceivers

- Ultra low power operation: 1.25 Watts typical

- Integrated serializer/deserializer, clock synthesis, clock recovery, and 8B/10B encode/decode logic

- Physical Coding Sublayer (PCS) logic for Gigabit Ethernet

- Optional receive FIFO which synchronizes incoming data to local clock domain