P4C150 Overview

Key Specifications

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Description

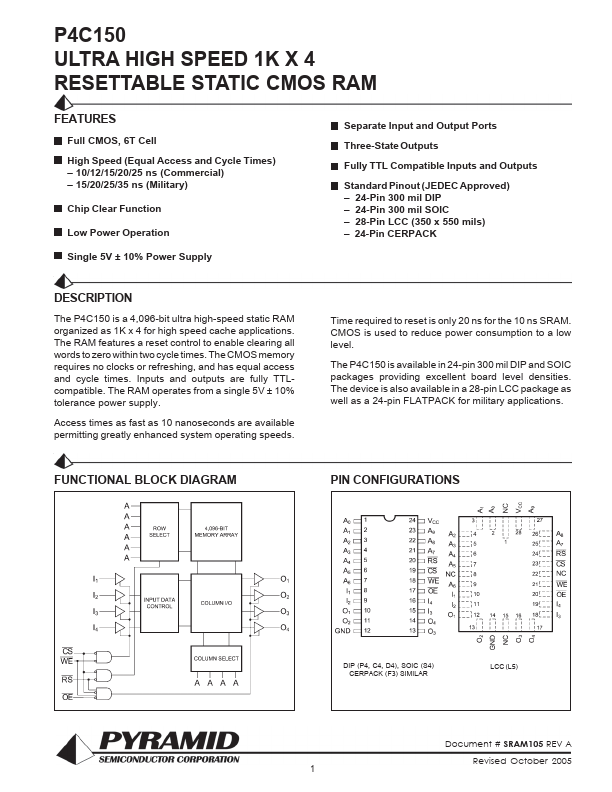

The P4C150 is a 4,096-bit ultra high-speed static RAM organized as 1K x 4 for high speed cache applications. The RAM features a reset control to enable clearing all words to zero within two cycle times.