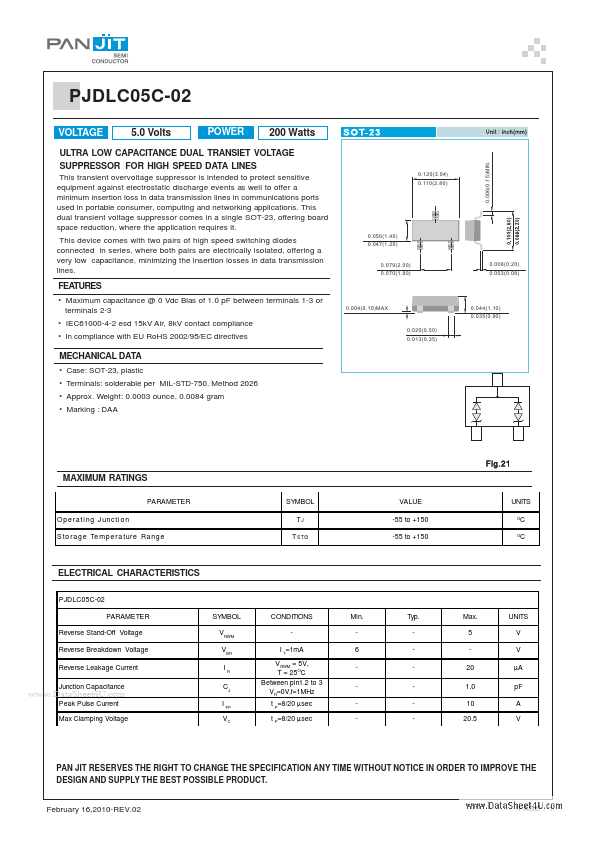

PJDLC05C-02

PJDLC05C-02 is ULTRA LOW CAPACITANCE DUAL TRANSIET VOLTAGE SUPPRESSOR manufactured by PanJit Semiconductor.

FEATURES

- Maximum capacitance @ 0 Vdc Bias of 1.0 p F between terminals 1-3 or terminals 2-3

- IEC61000-4-2 esd 15k V Air, 8k V contact pliance

- In pliance with EU Ro HS 2002/95/EC directives

0.004(0.10)MAX.

MECHANICAL DATA

- Case: SOT-23, plastic

- Terminals: solderable per MIL-STD-750, Method 2026

- Approx. Weight: 0.0003 ounce, 0.0084 gram

- Marking : DAA

Fig.21

MAXIMUM RATINGS

PARAMETER Op e ra ti ng J unc ti o n S to ra g e Te m p e ra ture Ra ng e SYMBOL TJ T S TG VALUE -55 to +150 -55 to +150 UNITS

ELECTRICAL CHARACTERISTICS

PJDLC05C-02 PARAMETER Reverse Stand-Off Voltage Reverse Breakdown Voltage Reverse Leakage Current Junction Capacitance Peak Pulse Current Max Clamping Voltage SYMBOL VRWM VBR IR CJ I PP VC CONDITIONS I T=1m A VRWM = 5V, T = 25OC Between pin1.2 to 3 VR=0V,f=1MHz t P=8/20 μsec t P=8/20 μsec Min. 6 Typ. Max. 5 20 1.0 10 20.5 UNITS V V μA p F A V

..

PAN JIT RESERVES THE RIGHT TO CHANGE THE SPECIFICATION ANY TIME WITHOUT NOTICE IN ORDER TO IMPROVE THE DESIGN AND SUPPLY THE BEST POSSIBLE PRODUCT.

February 16,2010-REV.02

PAGE . 1

Peak Pulse Current Ipp , A

Cap ac i tan c e CJ , p F

5 7 9 11 13 15 17 19 21 23 25

16 14 12 10 8 6 4 2 0

0.6 0.55 0.5 0.45 0.4 0.35 0.3 0 1 2 3 4 5

Clamping Voltage V C, V

FIG.1- TYPICAL CLAMPING VOLTAGE

Reverse Bias Voltage, V

FIG.2- TYPICAL JUNCTION CAPACITANCE UNDER BIAS

I R, Reverse Leakage Current( m A)

VR =5V

0.01...