PJDLLLC70

PJDLLLC70 is Very Low Capacitance Diode Array manufactured by PanJit Semiconductor.

FEATURES

Maximum Capacitance of 1.2p F at 0Vdc 1MHz Line-to-Ground Maximum Leakage Current of 1µA @ VRWM Industry Standard SMT Package SOT563 IEC61000-4-2 Full pliance; 15k V Air, 8k V Contact- 100% Tin Matte finish (LEAD-FREE PRODUCT)

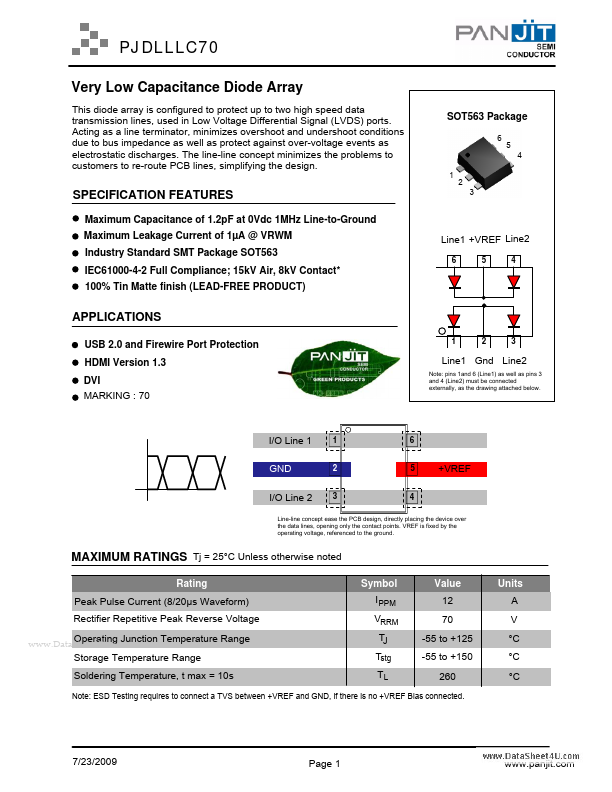

Line1 +VREF Line2

6 5 4

APPLICATIONS

USB 2.0 and Firewire Port Protection HDMI Version 1.3 DVI

1 2 3

Line1 Gnd Line2

Note: pins 1and 6 (Line1) as well as pins 3 and 4 (Line2) must be connected externally, as the drawing attached below.

MARKING : 70

I/O Line 1 GND I/O Line 2

+VREF

Line-line concept ease the PCB design, directly placing the device over the data lines, opening only the contact points. VREF is fixed by the operating voltage, referenced to the ground.

MAXIMUM RATINGS Tj = 25°C Unless otherwise noted

Rating Peak Pulse Current (8/20µs Waveform) Rectifier Repetitive Peak Reverse Voltage

..

Symbol I PPM VRRM TJ Tstg TL

Value 12 70 -55 to +125 -55 to +150 260

Units A V °C °C °C

Operating Junction Temperature Range Storage Temperature Range Soldering Temperature, t max = 10s

Note: ESD Testing requires to connect a TVS between +VREF and GND, if there is no +VREF Bias connected.

7/23/2009

Page 1

.panjit.

ELECTRICAL CHARACTERISTICS

Parameter Reverse Stand-Off Voltage Reverse Breakdown Voltage Reverse Leakage Current Diode Surge Forward Voltage (8/20µs) Diode Surge Forward Voltage (8/20µs) Diode Surge Forward Voltage (8/20µs) Off State Capacitance Symbol V RWM VBR IR VFC VFC VFC CT I BR = 50µA VR = 70V I pp = 1 A I pp = 5 A I pp = 12 A

0 Vdc Bias f = 1MHz Between I/O Line and GND 0 Vdc Bias f = 1MHz Between I/O lines

Tj = 25°C unless otherwise noted

Conditions Min Typical Max 70 85 1 2 7 13 1.0 1.0 Units V V µA V V V p F p F

..

7/23/2009

Page.2

.panjit....