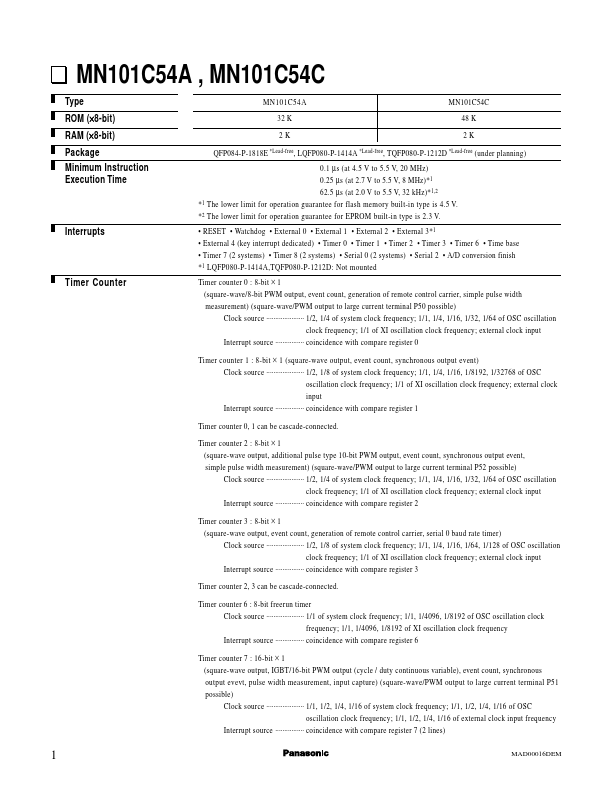

| Part | MN101C54 |

|---|---|

| Description | Lower limit for operation guarantee |

| Manufacturer | Panasonic |

| Size | 378.35 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MN101C54 | Matsushita Electric | MN101 Series microcontroller |

| MN101C539 | Panasonic | MICROCOMPUTER |

| MN101C58A | Matsushita Electric | MN101 Series microcontroller |

| MN101C57 | Matsushita Electric | MN101 Series microcontroller |

| MN101C589 | Matsushita Electric | MN101 Series microcontroller |