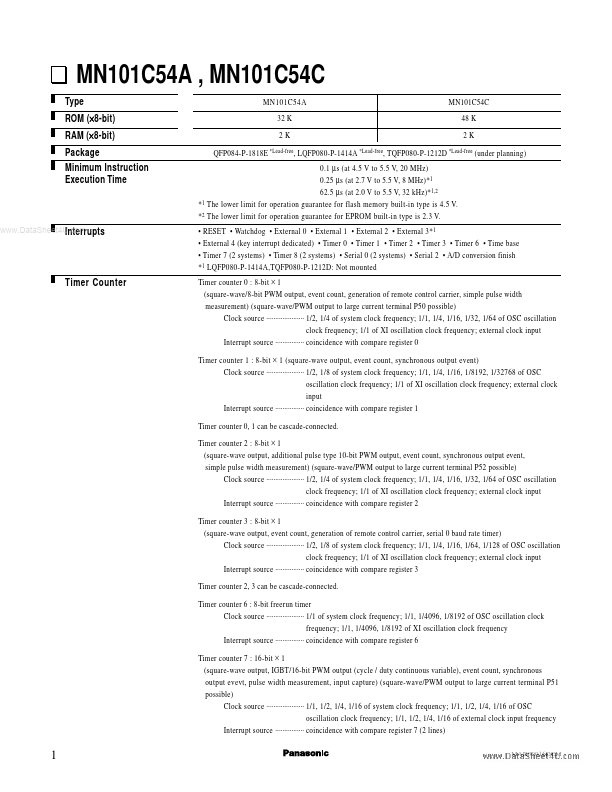

| Part | MN101CF54C |

|---|---|

| Description | Lower limit |

| Manufacturer | Panasonic |

| Size | 415.38 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MP9487 | Monolithic Power Systems | Switching Current Limit Step-Down Converter |

| HT7886 | HEROIC | Switching Current Limit Step-Down Converter |

| IEC947-5-1 | Schneider Electric | Limit Switches |