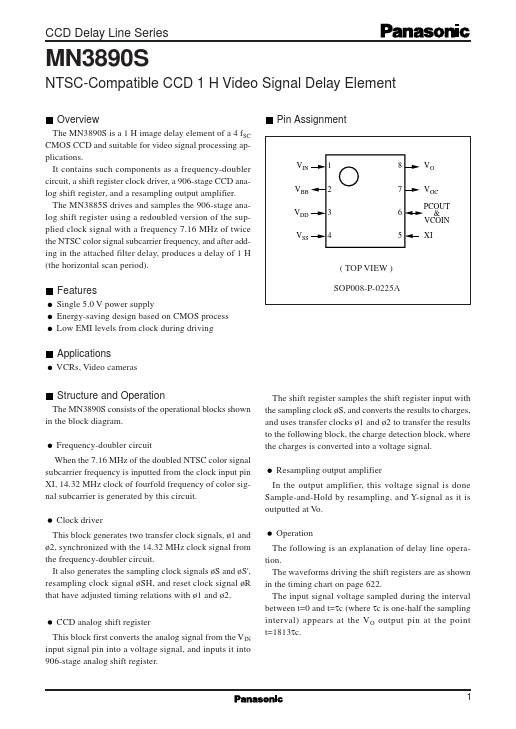

MN3890S

Key Features

- Single 5.0 V power supply Energy-saving design based on CMOS process Low EMI levels from clock during driving

Applications

- The input signal voltage sampled during the interval between t=0 and t=τc (where τc is one-half the sampling interval) appears at the V O output pin at the point t=1813τc