PI6C185-02B

PI6C185-02B is Precision 1-7 Clock Buffer manufactured by Pericom Semiconductor.

PI6C185-02B111222333444555666777888999000111222333444555666777888999000111222333444555666777888999000111222111222333444555666777888999000111222333444555666777888999000111222333444555666777888999000111222111222333444555666777888999000111222333444555666777888999000111222333444555666777888999000111222111222333444555666777888999000111222333444555666777888999000111222333444555666777888999000111222111222333444555666777888999000111222

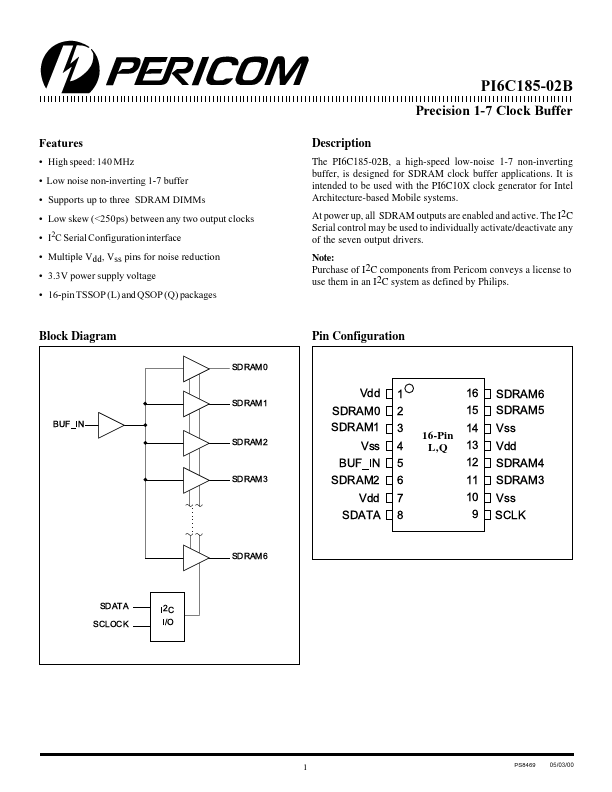

Precision 1-7 Clock Buffer

Features

High speed: 140 MHz Low noise non-inverting 1-7 buffer Supports up to three SDRAM DIMMs Low skew (<250ps) between any two output clocks I2C Serial Configuration interface Multiple Vdd, Vss pins for noise reduction ...