Datasheet Summary

Features

ÎÎ1:4 HCSL clock buffer ÎÎPCIe® Gen 1, 2 and 3 pliant ÎÎSelectable reference inputs ÎÎCycle-to-Cycle Jitter <70ps ÎÎOutput-to-Output Skew <35ps ÎÎ3.3V supply voltage ÎÎTSSOP-20 package ÎÎIndustrial Temperature

Applications

ÎÎServers ÎÎEmbedded puting systems ÎÎNetworking systems

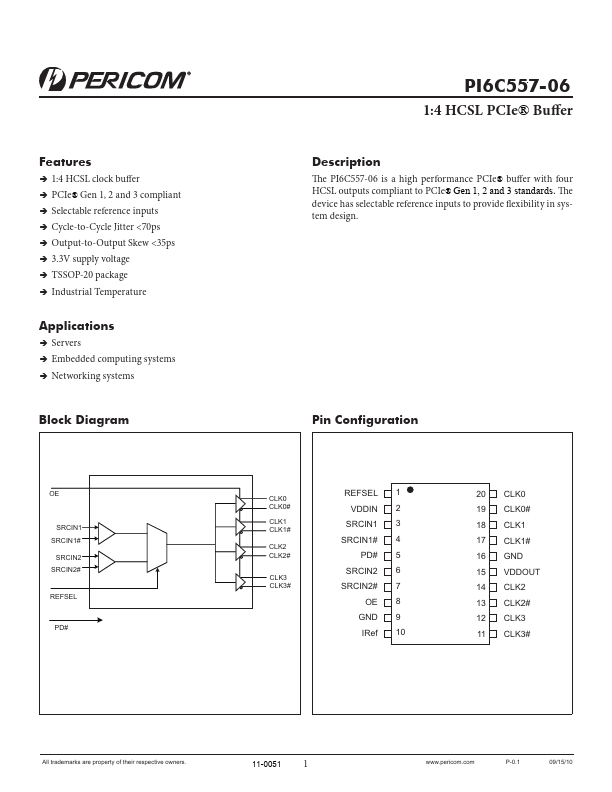

Block Diagram

SRCIN1 SRCIN1#

SRCIN2 SRCIN2#

REFSEL

PD#

1:4 HCSL PCIe® Buffer

Description

The PI6C557-06 is a high performance PCIe® buffer with four

HCSL outputs pliant to PCIe® Gen 1, 2 and 3 standards. The device has selectable reference inputs to provide flexibility in system design.

Pin Configuration

CLK0 CLK0#

CLK1 CLK1#

CLK2 CLK2#

CLK3 CLK3#

REFSEL VDDIN

SRCIN1 SRCIN1#

PD#...