Datasheet Summary

Features

ÎÎPhase jitter filter for PCIe® 2.0 application ÎÎFour pairs of HCSL PCIe 2.0 Differential Clocks ÎÎProp delay <± 250ps (in PLL mode) ÎÎLow skew < 50ps ÎÎLow jitter < 50ps cycle-to-cycle ÎÎ< 1 ps additive RMS phase jitter ÎÎ100 MHz PLL Mode operation ÎÎ3.3V operation ÎÎPackaging (Pb-free and Green):

àà 20-Pin 4.0mm x 4.0mm x0.75mm TQFN (ZD20)

1:4 PCI Express® Clock Driver

Description

Peri Semiconductor's PI6PCIEB24 is a PCI Express® (PCIe) 2.0 pliant high-speed, low-noise differential clock buffer. The device distributes the input differential PCIe clock to four differential pairs of clock outputs with zero delay PLL.

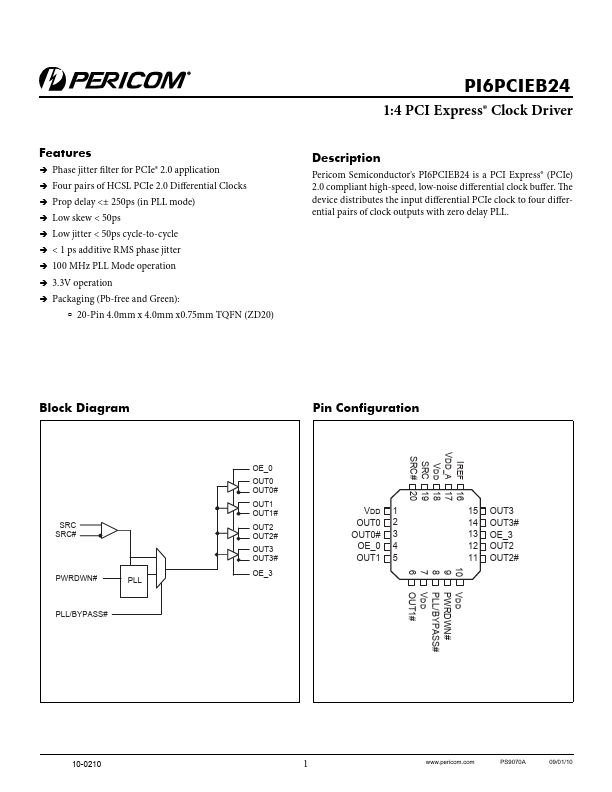

Block Diagram

SRC...