PL611S-28 Overview

Description

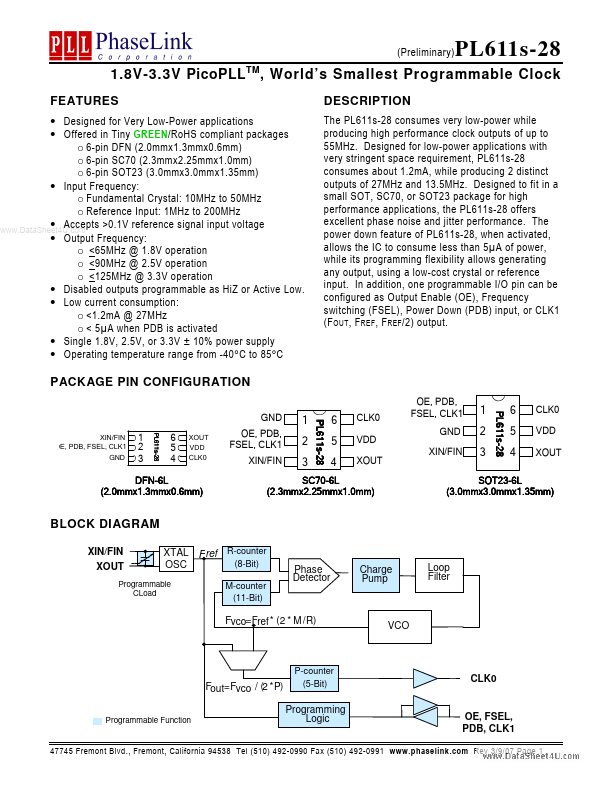

The PL611s-28 consumes very low-power while producing high performance clock outputs of up to 55MHz. Designed for low-power applications with very stringent space requirement, PL611s-28 consumes about 1.2mA, while producing 2 distinct outputs of 27MHz and 13.5MHz.

Key Features

- Designed for Very Low-Power applications

- Input Frequency: o Fundamental Crystal: 10MHz to 50MHz o Reference Input: 1MHz to 200MHz

- Accepts >0.1V reference signal input voltage

- Output Frequency: o <65MHz @ 1.8V operation o <90MHz @ 2.5V operation o <125MHz @ 3.3V operation

- Disabled outputs programmable as HiZ or Active Low