PLL103-01 Overview

Description

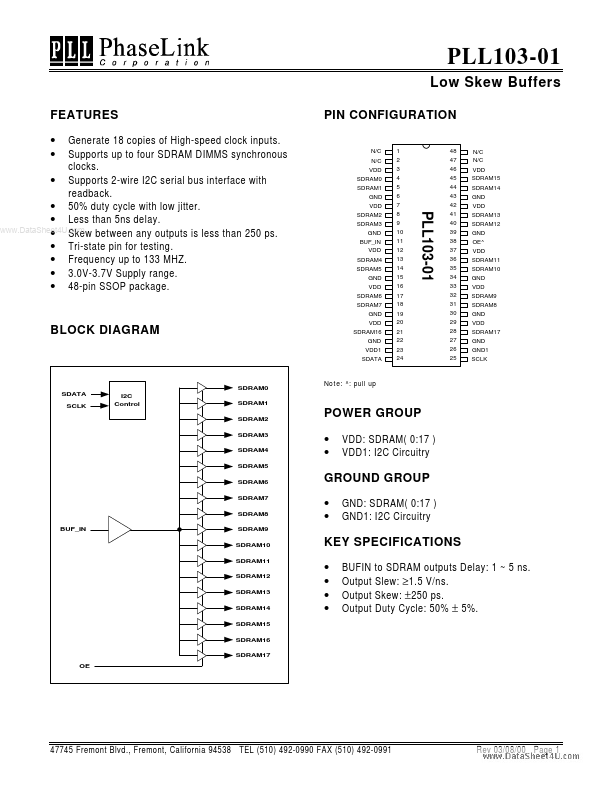

SDRAM (16:17) OE BUF_IN SDATA SCLK VDD VDD1 GND GND1 N/C Tristates all outputs, active low.

Key Features

- Supports 2-wire I2C serial bus interface with readback

- 50% duty cycle with low jitter

- Less than 5ns delay

- Skew between any outputs is less than 250 ps

- Tri-state pin for testing