PLL103-05 Overview

Description

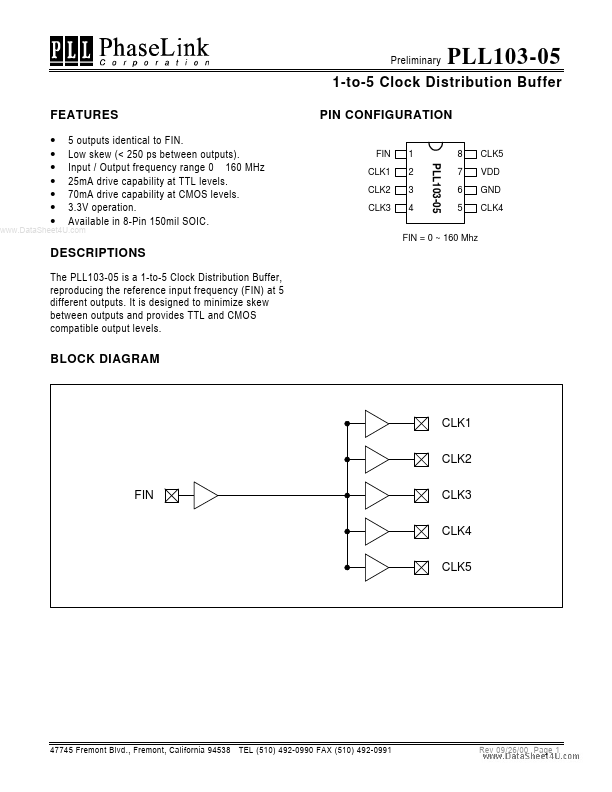

The PLL103-05 is a 1-to-5 Clock Distribution Buffer, reproducing the reference input frequency (FIN) at 5 different outputs. It is designed to minimize skew between outputs and provides TTL and CMOS compatible output levels.

Key Features

- 5 outputs identical to FIN

- Low skew (< 250 ps between outputs)

- Input / Output frequency range 0 – 160 MHz 25mA drive capability at TTL levels

- 70mA drive capability at CMOS levels

- Available in 8-Pin 150mil SOIC