PLL103-06 Overview

Description

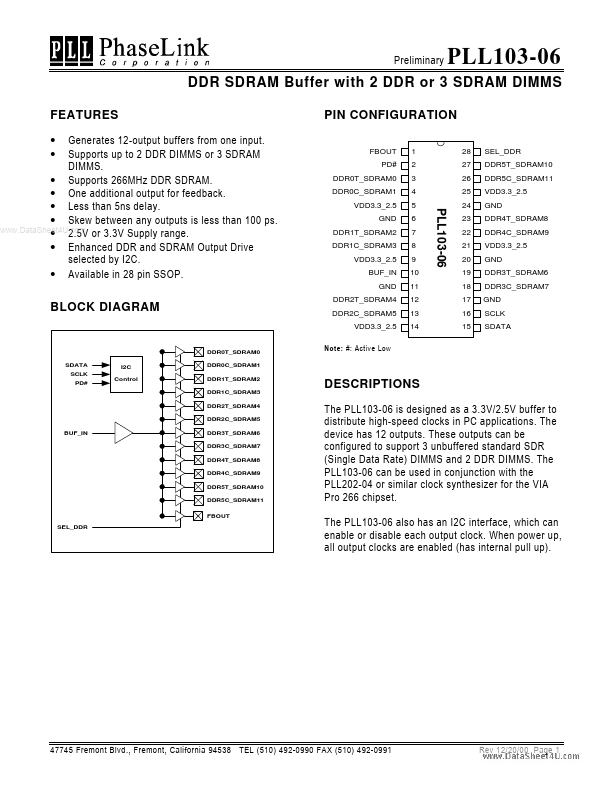

The PLL103-06 is designed as a 3.3V/2.5V buffer to distribute high-speed clocks in PC applications. The device has 12 outputs.

Key Features

- Supports 266MHz DDR SDRAM

- One additional output for feedback

- Less than 5ns delay

- Skew between any outputs is less than 100 ps

- 2.5V or 3.3V Supply range