PLL130-05 Overview

Description

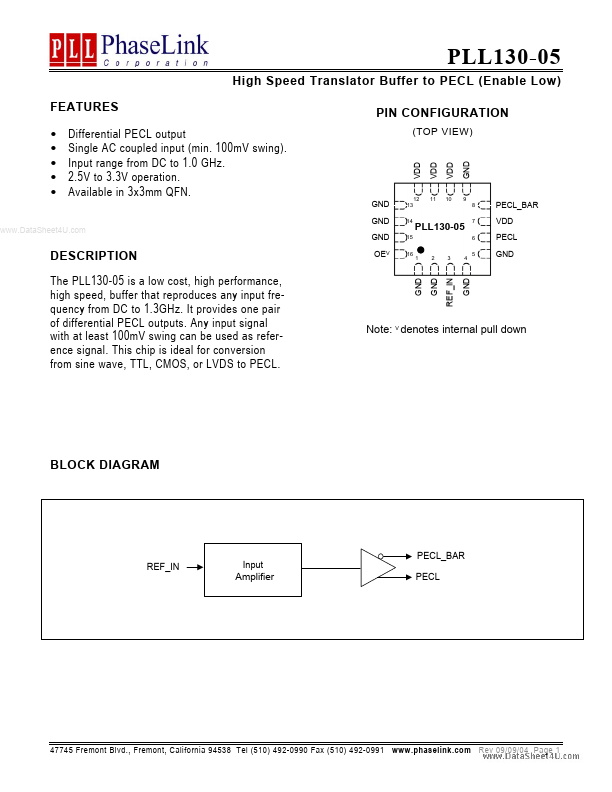

The PLL130-05 is a low cost, high performance, high speed, buffer that reproduces any input frequency from DC to 1.3GHz. It provides one pair of differential PECL outputs.

Key Features

- Differential PECL output Single AC coupled input (min

- Input range from DC to 1.0 GHz

- 2.5V to 3.3V operation

- Available in 3x3mm QFN