PLL130-69 Overview

Description

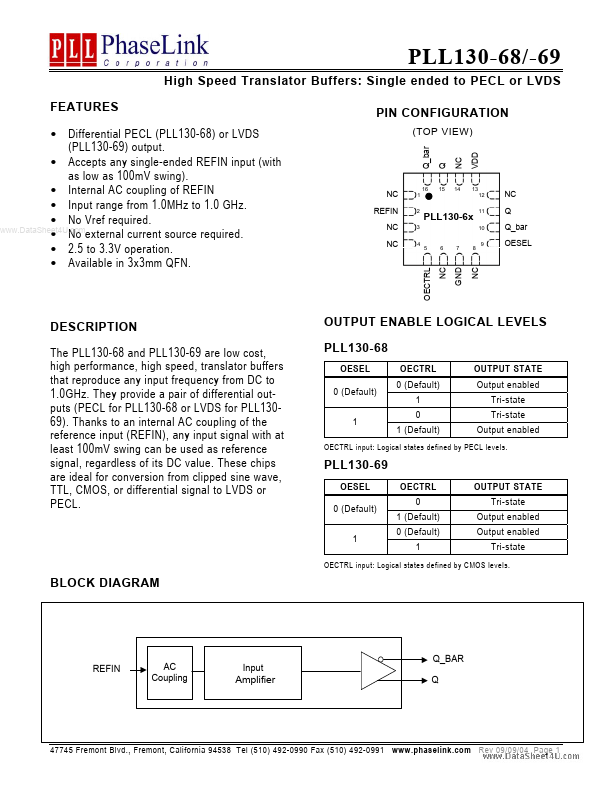

The PLL130-68 and PLL130-69 are low cost, high performance, high speed, translator buffers that reproduce any input frequency from DC to 1.0GHz. They provide a pair of differential outputs (PECL for PLL130-68 or LVDS for PLL13069).

Key Features

- Accepts any single-ended REFIN input (with as low as 100mV swing)

- Internal AC coupling of REFIN

- Input range from 1.0MHz to 1.0 GHz

- No Vref required

- No external current source required