PLL520-18 Overview

Description

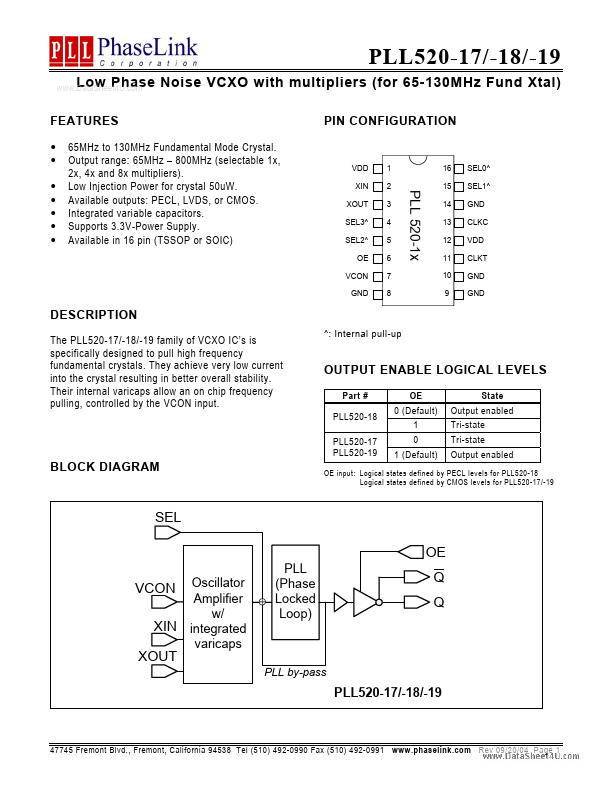

The PLL520-17/-18/-19 family of VCXO IC’s is specifically designed to pull high frequency fundamental crystals. They achieve very low current into the crystal resulting in better overall stability.

Key Features

- 65MHz to 130MHz Fundamental Mode Crystal

- Output range: 65MHz – 800MHz (selectable 1x, 2x, 4x and 8x multipliers)

- Low Injection Power for crystal 50uW

- Available outputs: PECL, LVDS, or CMOS

- Integrated variable capacitors