PLL521-23

PLL521-23 is Low Phase Noise PECL VCXO manufactured by PhaseLink Corporation.

FEATURES

- -

- -

- -

- -

- - 100MHz to 200MHz Fundamental Mode Crystal. Output range: 100MHz

- 200MHz. plementary PECL outputs. Selectable OE Logic (enable high or enable low). Integrated variable capacitors. High pull linearity: < 5%. +/- 120 ppm pull range Supports 2.5V or 3.3V-Power Supply. Available in 16-pin TSSOP and die form. Thickness 10 mil.

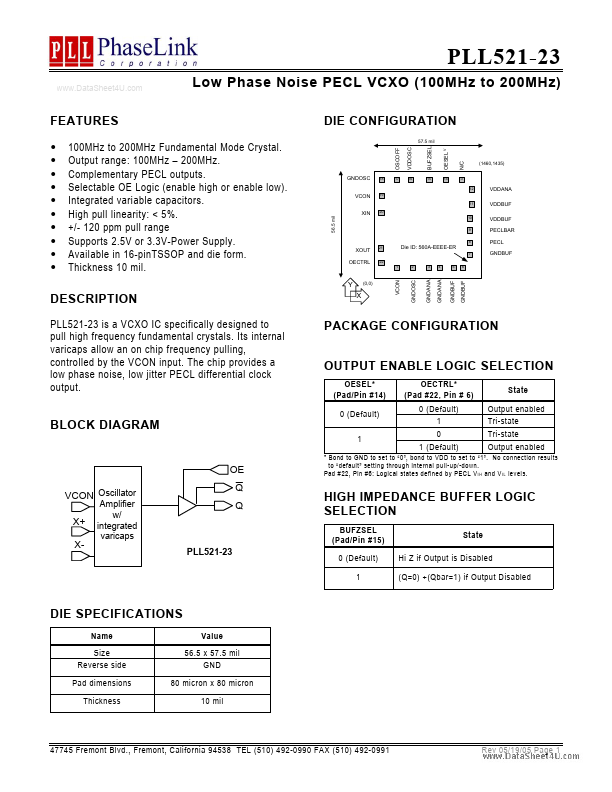

BUFZSEL

VDDOSC

OSCOFF

OESEL V

GNDOSC VCON XIN

N/C

(1460,1435)

13 12

VDDANA VDDBUF VDDBUF PECLBAR PECL GNDBUF

19 11 20 10 9 8

56.5 mil

XOUT OECTRL

Die ID: 560A-EEEE-ER

22 1 2 3 4 5 6

GNDANA

(0,0)

DESCRIPTION

PLL521-23 is a VCXO IC specifically designed to pull high frequency fundamental crystals. Its internal varicaps allow an on chip frequency pulling, controlled by the VCON input. The chip provides a low phase noise, low jitter PECL differential clock output.

PACKAGE CONFIGURATION OUTPUT ENABLE LOGIC SELECTION

OESEL- (Pad/Pin #14) 0 (Default) 1 OECTRL- (Pad #22, Pin # 6) 0 (Default) 1 0 1 (Default) State Output enabled Tri-state Tri-state Output enabled

BLOCK DIAGRAM

OE VCON Oscillator X+ XQ Q

Amplifier w/ integrated varicaps

- Bond to GND to set to “0”, bond to VDD to set to “1”. No connection results to “default” setting through internal pull-up/-down. Pad #22, Pin #6: Logical states defined by PECL V I H and V I L levels.

HIGH IMPEDANCE BUFFER LOGIC...