PLL52C61-23 Overview

Description

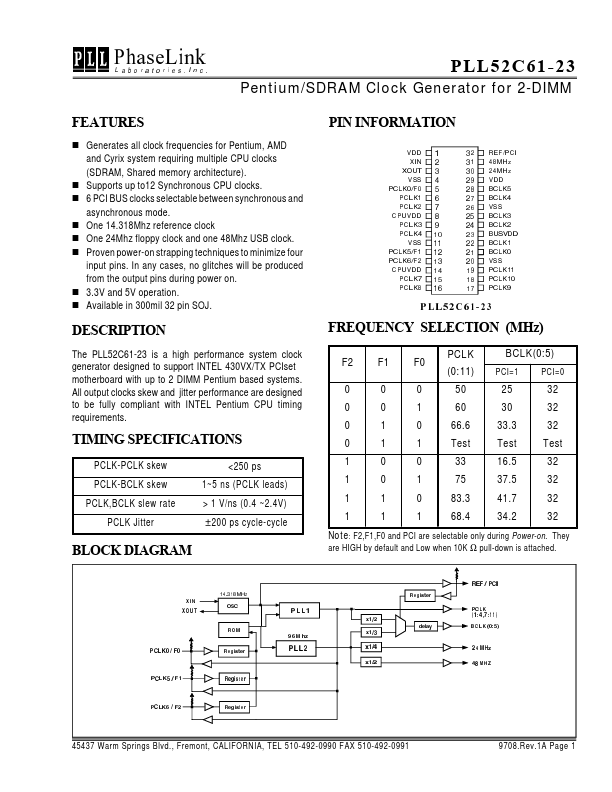

The PLL52C61-23 is a high performance system clock generator designed to support INTEL 430VX/TX PCIset motherboard with up to 2 DIMM Pentium based systems. All output clocks skew and jitter performance are designed to be fully compliant with INTEL Pentium CPU timing requirements.

Key Features

- Supports up to12 Synchronous CPU clocks. n 6 PCI BUS clocks selectable between synchronous and asynchronous mode

- One 14.318Mhz reference clock

- One 24Mhz floppy clock and one 48Mhz USB clock

- Available in 300mil 32 pin SOJ