PLL601-01 Overview

Description

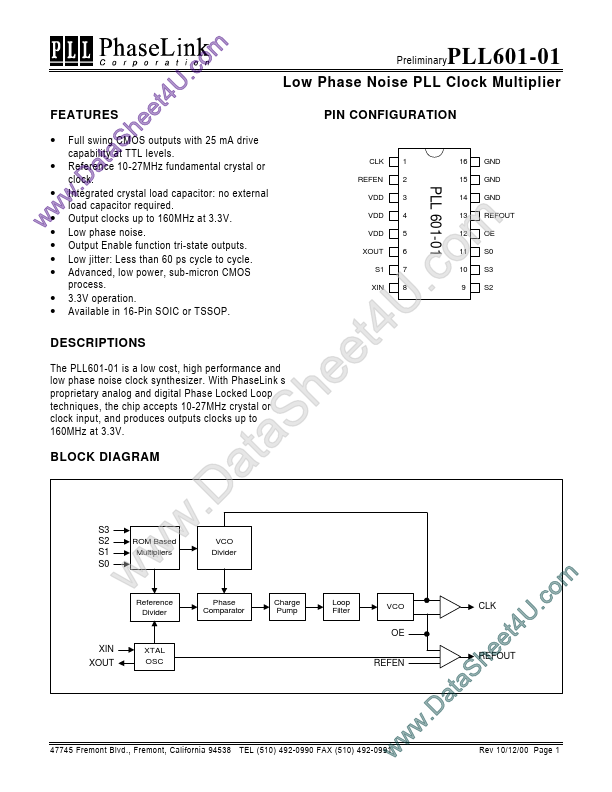

The PLL601-01 is a low cost, high performance and low phase noise clock synthesizer. With PhaseLink’s proprietary analog and digital Phase Locked Loop techniques, the chip accepts 10-27MHz crystal or clock input, and produces outputs clocks up to 160MHz at 3.3V.

Key Features

- Full swing CMOS S outputs with 25 mA drive capability a at TTL levels. t 10-27MHz fundamental crystal or

- Reference a clock. .D crystal load capacitor: no external

- Integrated w load capacitor required. w

- Output clocks up to 160MHz at 3.3V. w

- Low phase noise