PLL602-04 Overview

Description

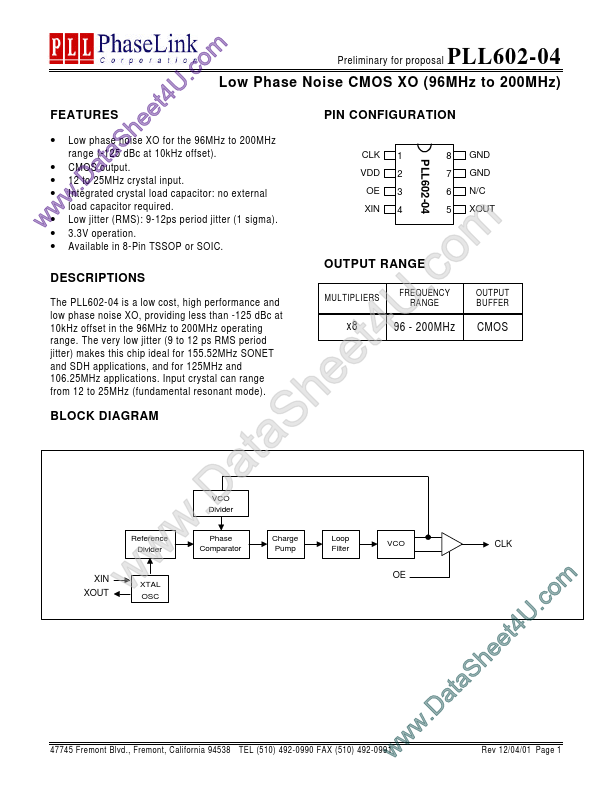

The PLL602-04 is a low cost, high performance and low phase noise XO, providing less than -125 dBc at 10kHz offset in the 96MHz to 200MHz operating range. The very low jitter (9 to 12 ps RMS period jitter) makes this chip ideal for 155.52MHz SONET and SDH applications, and for 125MHz and 106.25MHz applications.