PLL650-03 Overview

Description

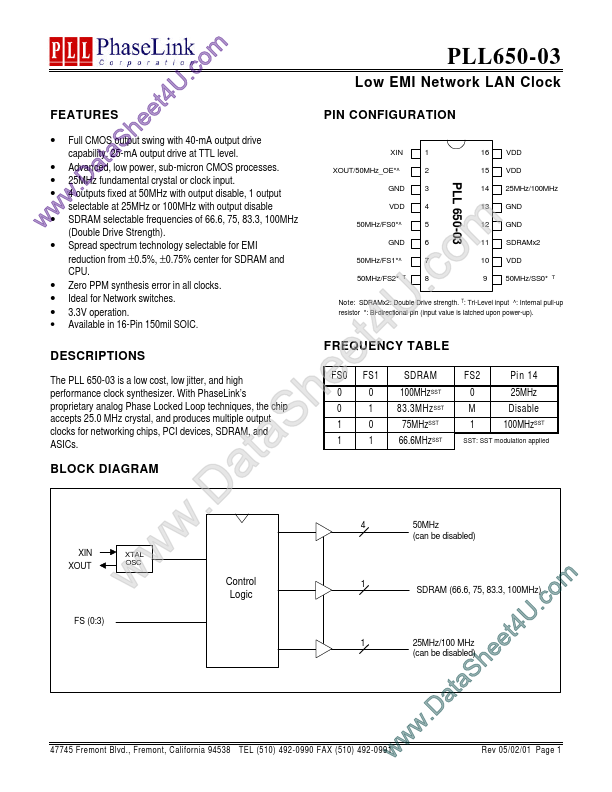

The PLL 650-03 is a low cost, low jitter, and high performance clock synthesizer. With PhaseLink’s proprietary analog Phase Locked Loop techniques, the chip accepts 25.0 MHz crystal, and produces multiple output clocks for networking chips, PCI devices, SDRAM, and ASICs.

Key Features

- Full CMOS output swing with 40-mA output drive S output capability. 25-mA drive at TTL level. a t

- Advanced, low power, sub-micron CMOS processes. a

- 25MHz .D fundamental crystal or clock input

- 4 outputs fixed at 50MHz with output disable, 1 output w selectable at 25MHz or 100MHz with output disable w

- SDRAM selectable frequencies of 66.6, 75, 83.3, 100MHz w (Double Drive Strength)