AN7187 Overview

Key Features

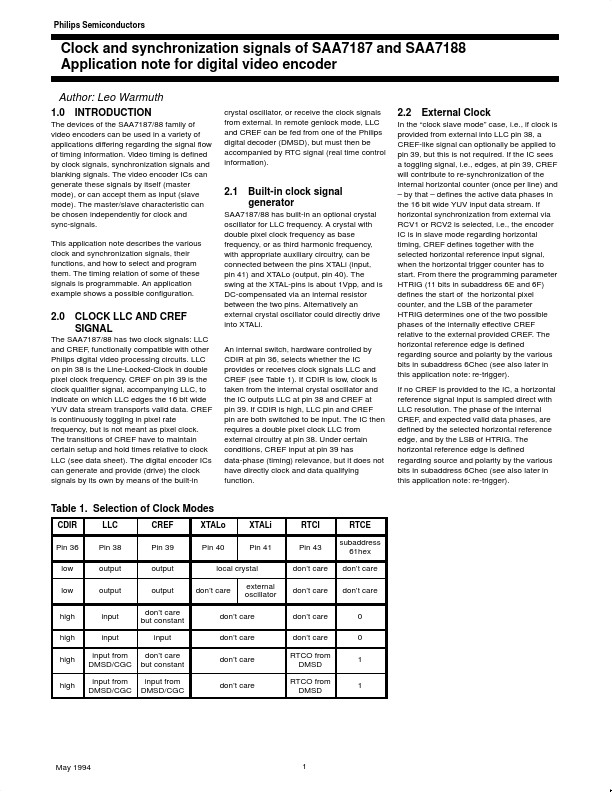

- defines the active data phases in the 16 bit wide YUV input data stream. If horizontal synchronization from external via RCV1 or RCV2 is selected, i.e., the encoder IC is in slave mode regarding horizontal timing, CREF defines together with the selected horizontal reference input signal, when the horizontal trigger counter has to start. From there the programming parameter HTRIG (11 bits in subaddress 6E and 6F) defines the start of the horizontal pixel counter, and the LSB of the parameter HTRIG determines one of the two possible ph