NE5537N

NE5537N is Sample-and-hold amplifier manufactured by Philipss.

Philips Semiconductors Linear Products

Product specification

Sample-and-hold amplifier

NE/SE5537

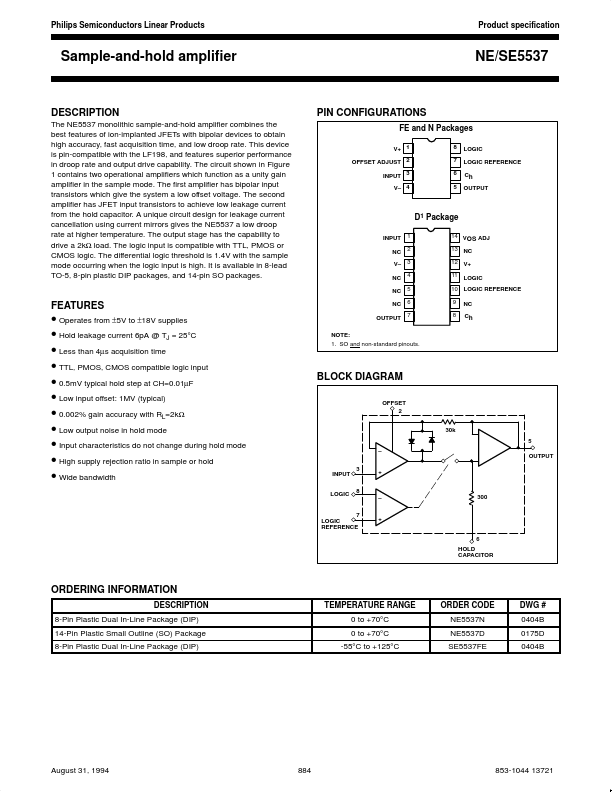

DESCRIPTION

The NE5537 monolithic sample-and-hold amplifier bines the best Features of ion-implanted JFETs with bipolar devices to obtain high accuracy, fast acquisition time, and low droop rate. This device is pin-patible with the LF198, and Features superior performance in droop rate and output drive capability. The circuit shown in Figure 1 contains two operational amplifiers which function as a unity gain amplifier in the sample mode. The first amplifier has bipolar input transistors which give the system a low offset voltage. The second amplifier has JFET input transistors to achieve low leakage current from the hold capacitor. A unique circuit design for leakage current cancellation using current mirrors gives the NE5537 a low droop rate at higher temperature. The output stage has the capability to drive a 2kΩ load. The logic input is patible with TTL, PMOS or CMOS logic. The differential logic threshold is 1.4V with the sample mode occurring when the logic input is high. It is available in 8-lead TO-5, 8-pin plastic DIP packages, and 14-pin SO packages.

PIN CONFIGURATIONS

FE and N Packages

V+ 1 OFFSET ADJUST 2 INPUT 3 V- 4 8 7 6 5 LOGIC LOGIC REFERENCE Ch OUTPUT

D1 Package

INPUT NC V- NC NC 1 2 3 4 5 6 7 14 V OS ADJ 13 NC 12 V+ 11 LOGIC 10 LOGIC REFERENCE 9 8 NC Ch

Features

NC OUTPUT

- Operates from ±5V to ±18V supplies

- Hold leakage current 6p A @ TJ = 25°C

- Less than 4µs acquisition time

- TTL, PMOS, CMOS patible logic input

- 0.5m V typical hold step at CH=0.01µF

- Low input offset: 1MV (typical)

- 0.002% gain accuracy with RL=2kΩ

- Low output noise in hold mode

- Input characteristics do not change during hold mode

- High supply rejection ratio in sample or hold

- Wide bandwidth

NOTE: 1. SO and non-standard pinouts.

BLOCK DIAGRAM

OFFSET 2 30k 5

- 3 + OUTPUT

INPUT LOGIC

- +...