QL1P075

QL1P075 is Ultra-Low Power FPGA Combining Performance manufactured by QuickLogic.

..

Quick Logic Polar Pro™ Data Sheet

- -

- -

- - bining Low Power, Performance, Density, and Embedded RAM Device Highlights

Flexible Programmable Logic

- 0.18 µm, six layer metal CMOS process

- 1.8 V core voltage, 1.8/2.5/3.3 V drive capable I/Os

- Up to 202 kilobits of SRAM

- Up to 292 I/Os available

- Up to one million system gates

- Nonvolatile, instant-on

- IEEE 1149.1 boundary scan testing pliant

- Quadrant-based segmentable clock networks

20 quad clock networks per device 4 quad clock networks per quadrant 1 dedicated clock network per quadrant

- Two user Configurable Clock Managers (CCMs)

Very Low Power (VLP) Mode

- Quick Logic Polar Pro has a special VLP pin which can enable a low power sleep mode that significantly reduces the overall power consumption of the device.

- Enter VLP mode from normal operation in less than 250 µs

- Exit from VLP mode to normal operation in less than 250 µs

Embedded Dual Port SRAM

- Up to eight dual-port 4-kilobit high performance SRAM blocks

- Embedded synchronous/asynchronous FIFO controller

- Configurable and cascadable aspect ratio

Security Links

There are several security links to disable JTAG access to the device. Programming these optional links pletely disables access to the device from the outside world and provides an extra level of design security not possible in SRAM-based FPGAs.

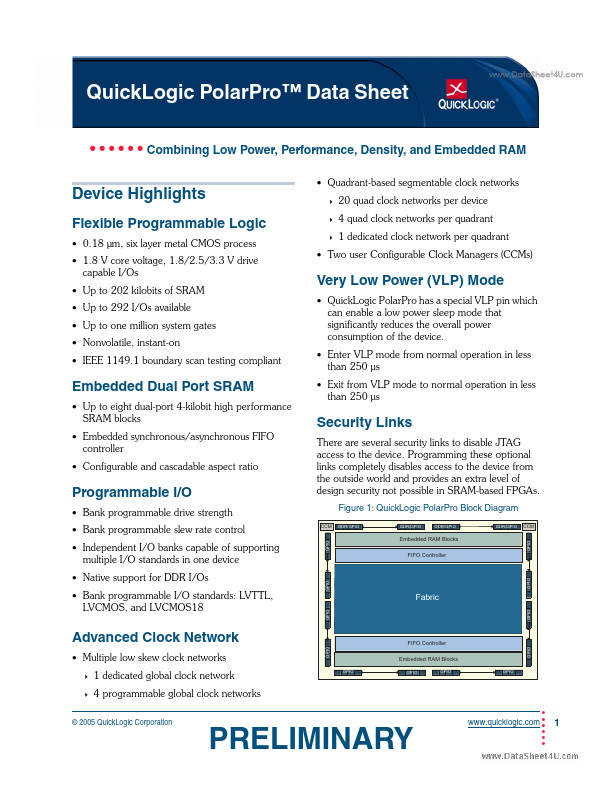

Figure 1: Quick Logic Polar Pro Block Diagram

GPIO DDR/GPIO DDR/GPIO DDR/GPIO DDR/GPIO

Programmable...