VRS51L3074

VRS51L3074 is FRAM-enhanced high performance 8051-based microcontroller coupled manufactured by Ramtron Corporation.

..

9 SPI Interface

The SPI interface of the VRS51L3074’s provides numerous enhancements pared to other vendor offerings. The SPI interface’s key Features include:

- -

- -

- -

- - Supports four standard SPI modes (clock phase/polarity) Operates in master and slave modes Automatic control of up to four chip select lines Configurable transaction size (1 to 32 bits) Transaction size of >32 bits is possible Double Rx and TX data buffers Configurable MSB or LSB first transaction Generation frame select/load signals

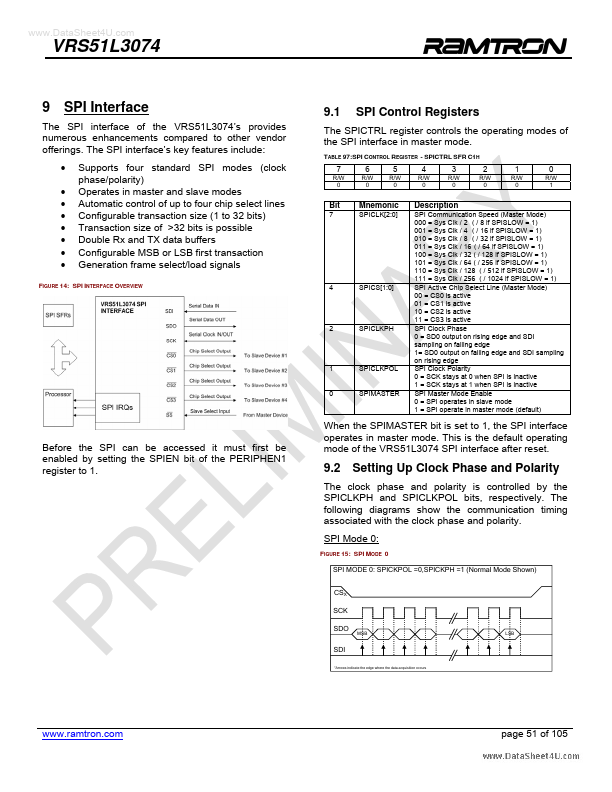

SPI Control Registers

The SPICTRL register controls the operating modes of the SPI interface in master mode.

TABLE 97:SPI CONTROL REGISTER

-...