HD74LS165AP

HD74LS165AP is Parallel-Load 8-bit Shift Register manufactured by Renesas.

- Part of the HD74LS165A comparator family.

- Part of the HD74LS165A comparator family.

feature gated clock inputs and plementary outputs from the eighth bit. All inputs are diode-clamped to minimize transmission-line effects, thereby simplifying system design.

Clocking is acplished through a 2-input positive-NOR gate, permitting one input to be used as a clock-inhibit function. Holding either of the clock inputs high inhibits clocking and holding either clock input low with the shift / load input high enables the other clock input. The clock-inhibit input should be changed to the high level only while the clock input is high. Parallel loading is inhibited as long as the shift / load input is high. Data at the parallel inputs are loaded directly into the register on a high-to-low transition of the shift / load input independently of the levels of the clock, clock inhibit, or serial inputs.

Features

- Ordering Information

Part Name

Package Type

Package Code (Previous Code)

Package Abbreviation

DILP-16 pin

PRDP0016AE-B

(DP-16FV)

HD74LS165AFPEL SOP-16 pin (JEITA)

PRSP0016DH-B

(FP-16DAV)

Note: Please consult the sales office for the above package availability.

Taping Abbreviation (Quantity)

- EL (2,000 pcs/reel)

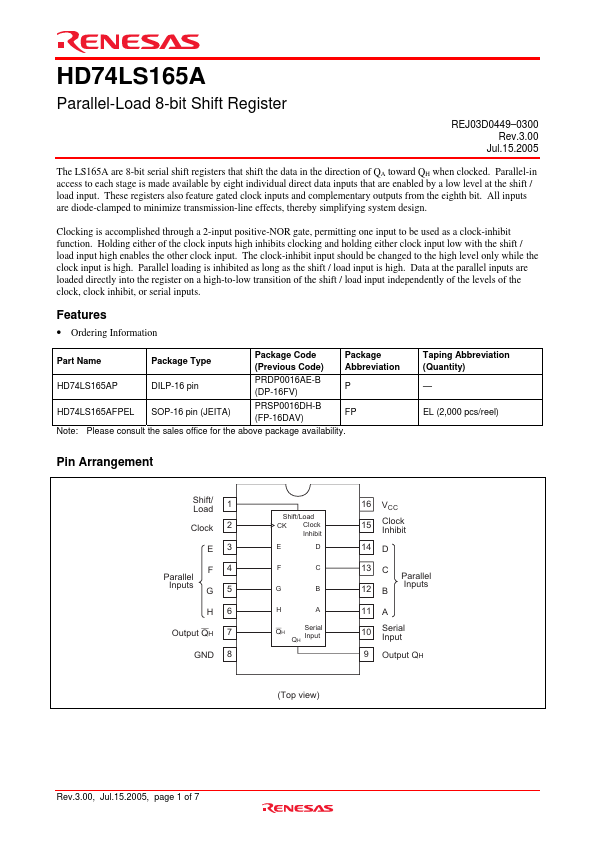

Pin Arrangement

Shift/ Load

Clock 2

E3

F4 Parallel

Inputs G 5

H6

Output QH 7

GND 8

Shift/Load CK...