HD74LV1G125A

HD74LV1G125A is Bus Buffer Gate manufactured by Renesas.

scription

The HD74LV1G125A has a bus buffer gate with 3- state output in a 5 pin package. Output is disabled when the associated output enable (OE) input is high. To ensure the high impedance state during power up or power down, OE should be connected to VCC through a pull-down resistor; the minimum value of the resistor is determined by the current sourcing capability of the driver. Low voltage and high-speed operation is suitable for the battery powered products (e.g., notebook puters), and the low power consumption extends the battery life.

Features

- The basic gate function is lined up as Renesas uni logic series.

- Supplied on emboss taping for high-speed automatic mounting.

- Electrical characteristics equivalent to the HD74LV125A Supply voltage range : 1.65 to 5.5 V Operating temperature range :

- 40 to +85°C

- All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VO (Max.) = 5.5 V (@VCC = 0 V, Output : Z)

- Output current ±6 m A (@VCC = 3.0 V to 3.6 V), ±12 m A (@VCC = 4.5 V to 5.5 V)

- All the logical input has hysteresis voltage for the slow transition.

- Ordering Information

Part Name HD74LV1G125ACME HD74LV1G125AVSE Note: Package Type CMPAK- 5 pin VSON- 5 pin Package Code (Previous Code) PTSP0005ZC-A (CMPAK-5V) PUSN0005KA-A (TNP-5DV) Package Abbreviation CM VS Taping Abbreviation (Quantity) E (3000 pcs/reel) E (3000 pcs/reel)

Please consult the sales office for the above package availability.

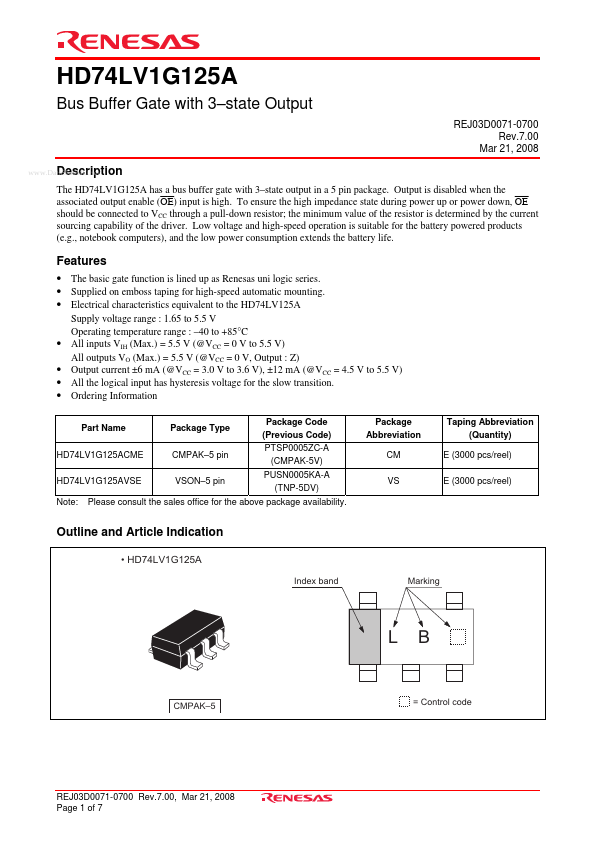

Outline and Article Indication

- HD74LV1G125A

Index band Marking

CMPAK- 5

= Control code

REJ03D0071-0700 Rev.7.00, Mar 21, 2008 Page 1 of 7

Outline and Article Indication

- HD74LV1G125A

Marking

VSON- 5

= Control code

Function Table

Inputs OE L L H H : High level L : Low level X : Immaterial Z : High impedance A H L X Output Y H L Z

Pin Arrangement

(Top view)

REJ03D0071-0700 Rev.7.00, Mar 21, 2008 Page 2 of 7

Absolute Maximum...