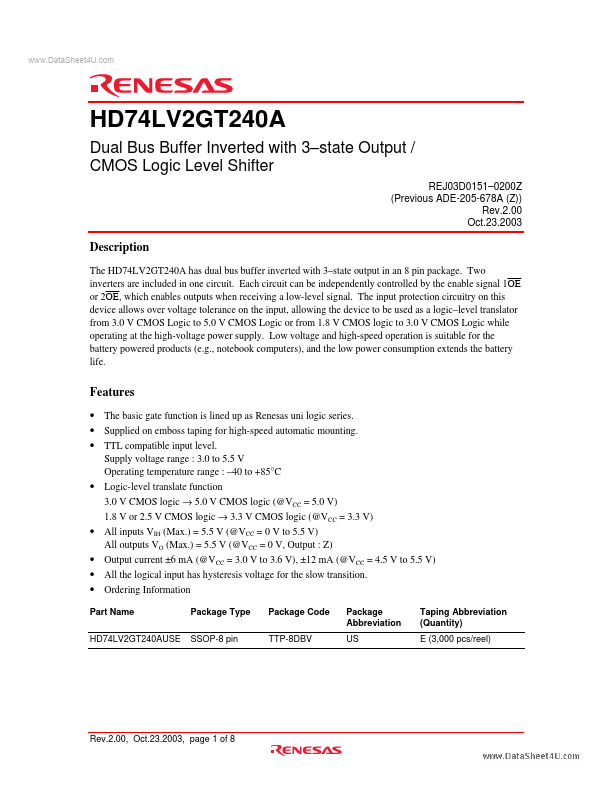

HD74LV2GT240A

HD74LV2GT240A is Dual Bus Buffer Inverted manufactured by Renesas.

..

Dual Bus Buffer Inverted with 3- state Output / CMOS Logic Level Shifter

REJ03D0151- 0200Z (Previous ADE-205-678A (Z)) Rev.2.00 Oct.23.2003

Description

The HD74LV2GT240A has dual bus buffer inverted with 3- state output in an 8 pin package. Two inverters are included in one circuit. Each circuit can be independently controlled by the enable signal 1OE or 2OE, which enables outputs when receiving a low-level signal. The input protection circuitry on this device allows over voltage tolerance on the input, allowing the device to be used as a logic- level translator from 3.0 V CMOS Logic to 5.0 V CMOS Logic or from 1.8 V CMOS logic to 3.0 V CMOS Logic while operating at the high-voltage power supply. Low voltage and high-speed operation is suitable for the battery powered products (e.g., notebook puters), and the low power consumption extends the battery life.

Features

- The basic gate function is lined up as Renesas uni logic series.

- Supplied on emboss taping for high-speed automatic mounting.

- TTL patible input level. Supply voltage range : 3.0 to 5.5 V Operating temperature range :

- 40 to +85°C

- Logic-level translate function 3.0 V CMOS logic → 5.0 V CMOS logic (@VCC = 5.0 V) 1.8 V or 2.5 V CMOS logic → 3.3 V CMOS logic (@VCC = 3.3 V)

- All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VO (Max.) = 5.5 V (@VCC = 0 V, Output : Z)

- Output current ±6 m A (@VCC = 3.0 V to 3.6 V), ±12 m A (@VCC = 4.5 V to 5.5 V)

- All the logical input has hysteresis voltage for the slow transition.

- Ordering Information

Part Name HD74LV2GT240AUSE Package Type SSOP-8 pin Package Code TTP-8DBV Package Abbreviation US Taping Abbreviation (Quantity) E (3,000 pcs/reel)

Rev.2.00, Oct.23.2003, page 1 of 8

..

Outline and Article Indication

- HD74LV2GT240A

Index band Lot No.

Y M W T 4 0

SSOP-8 Marking

Y : Year code (the last digit of year) M : Month code W : Week code

Function Table

Inputs OE L L H H :...