RD74LVC126B

RD74LVC126B is manufactured by Renesas.

..

Quad. Bus Buffer Gates with 3-state Outputs

REJ03D0499- 0200 Rev.2.00 Dec. 10, 2004

Description

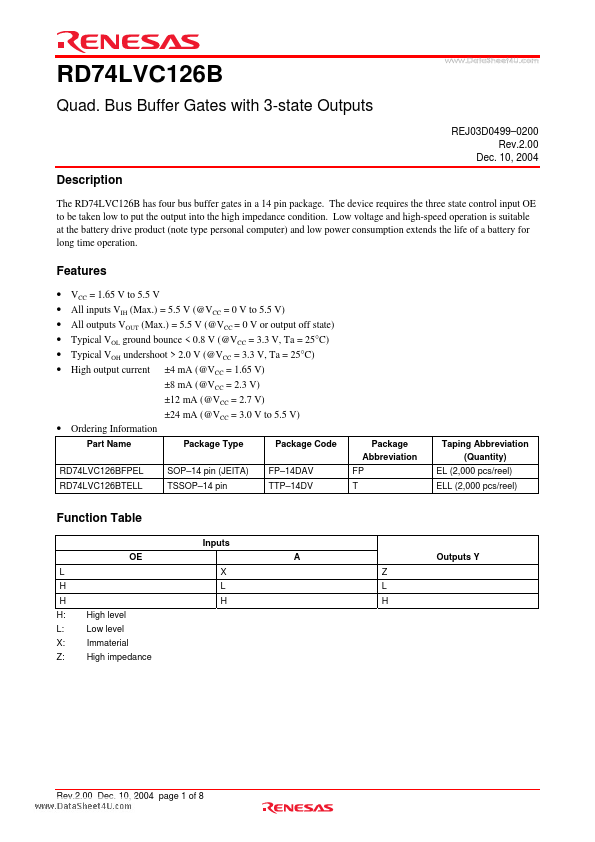

The RD74LVC126B has four bus buffer gates in a 14 pin package. The device requires the three state control input OE to be taken low to put the output into the high impedance condition. Low voltage and high-speed operation is suitable at the battery drive product (note type personal puter) and low power consumption extends the life of a battery for long time operation.

Features

VCC = 1.65 V to 5.5 V All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VOUT (Max.) = 5.5 V (@VCC = 0 V or output off state) Typical VOL ground bounce < 0.8 V (@VCC = 3.3...