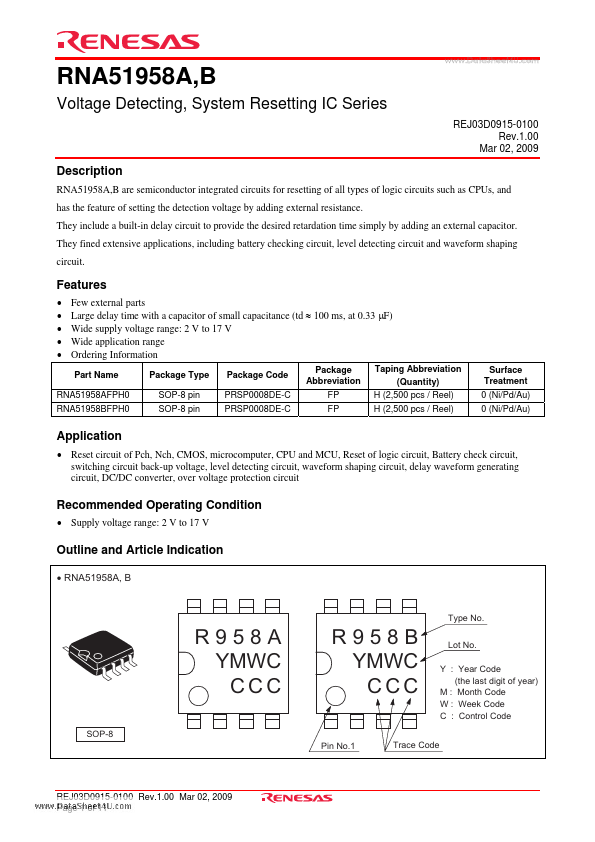

RNA51958B Overview

Key Specifications

Package: DIP

Mount Type: Through Hole

Pins: 8

Height: 5.06 mm

Description

RNA51958A,B are semiconductor integrated circuits for resetting of all types of logic circuits such as CPUs, and has the feature of setting the detection voltage by adding external resistance. They include a built-in delay circuit to provide the desired retardation time simply by adding an external capacitor.