70T3799M

Description

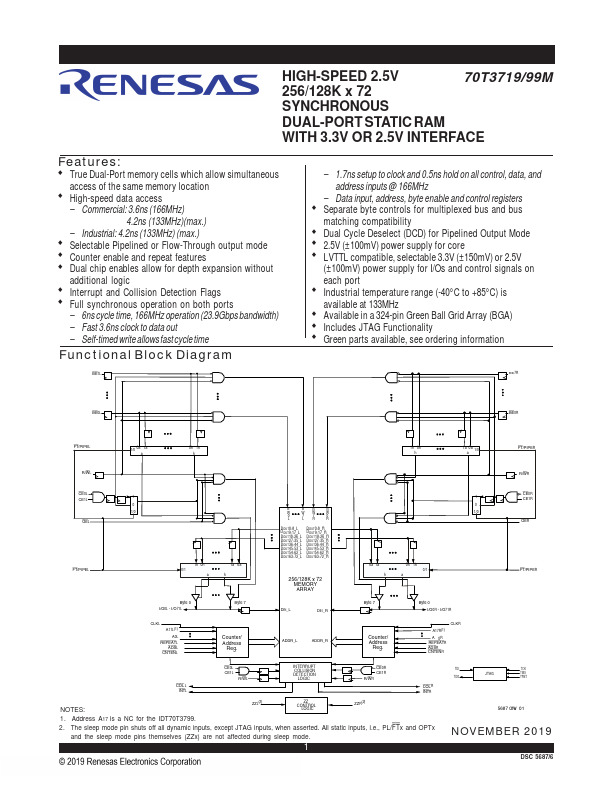

The IDT70T3719/99M is a high-speed 256K/128K x 72 bit synchronous Dual-Port RAM. The memory array utilizes Dual-Port memory cells to allow simultaneous access of any address from both ports.

Key Features

- True Dual-Port memory cells which allow simultaneous access of the same memory location

- High-speed data access – mercial: 3.6ns (166MHz) 4.2ns (133MHz)(max.) – Industrial: 4.2ns (133MHz) (max.)

- Selectable Pipelined or Flow-Through output mode

- Counter enable and repeat features

- Dual chip enables allow for depth expansion without additional logic

- Interrupt and Collision Detection Flags