72V3612

72V3612 is 3.3 VOLT CMOS SyncBiFIFO manufactured by Renesas.

FEATURES

:

- Two independent clocked FIFOs (64 x 36 storage capacity each) buffering data in opposite directions

- Supports clock frequencies up to 83 MHz

- Fast access times of 8ns

- Free-running CLKA and CLKB can be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted)

- Mailbox bypass Register for each FIFO

- Programmable Almost-Full and Almost-Empty Flags

- Microprocessor interface control logic

- EFA , FFA , AEA , and AFA flags synchronized by CLKA

- EFB , FFB , AEB , and AFB flags synchronized by CLKB

- Passive parity checking on each port

- Parity generation can be selected for each port

- Available in space saving 120-pin thin quad flat package (TQFP)

- Green parts available, see ordering information

DESCRIPTION

:

The IDT72V3612 is designed to run off a 3.3V supply for exceptionally lowpower consumption. This device is a monolithic high-speed, low-power CMOS bi-directional clocked FIFO memory. It supports clock frequencies up to 83 MHz and has read access times as fast as 8ns. The FIFO operates in IDT Standard mode. Two independent 64 x 36 dual-port SRAM FIFOs on board the chip buffer data in opposite directions. Each FIFO has flags to indicate empty and full conditions and two programmable flags (Almost-Full and Almost-Empty) to

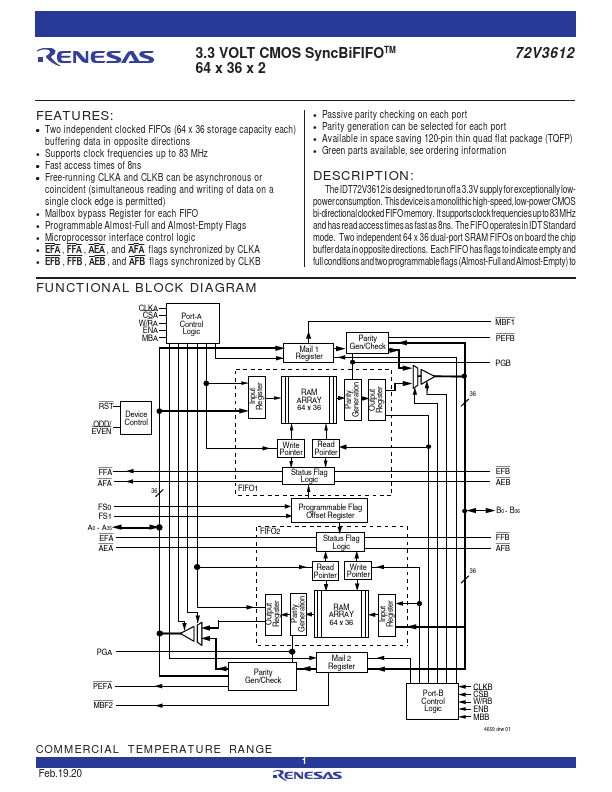

FUNCTIONAL BLOCK DIAGRAM

CLKA CSA

W/RA ENA MBA

Port-A Control Logic

Mail 1 Register

Parity Gen/Check

MBF1 PEFB

Input Register Parity Generation Output Register

RST ODD/ EVEN

Device Control

FFA AFA

FS0 FS1 A0

- A35 EFA AEA

RAM ARRAY 64 x 36

FIFO1

Write Read Pointer Pointer

Status Flag Logic

FIFO2

Programmable Flag Offset Register

Status Flag...