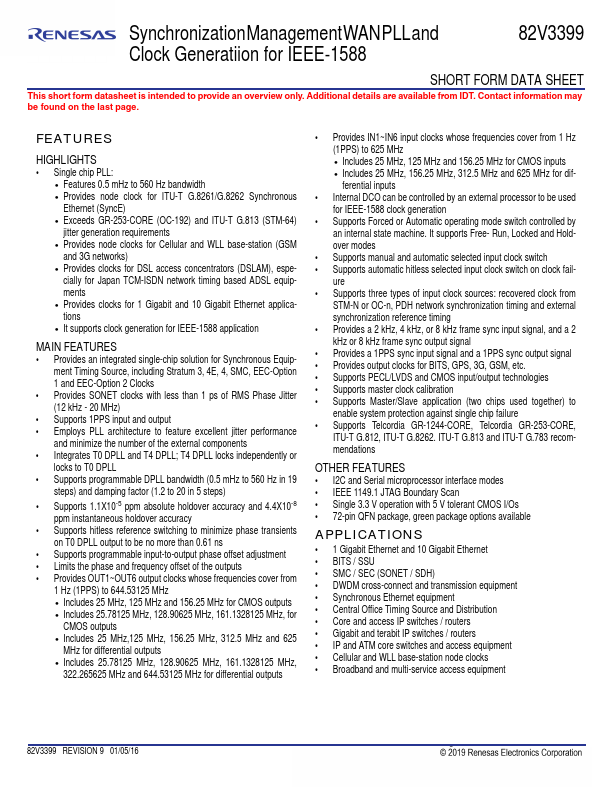

82V3399

overview only. Additional details are available from IDT. Contact information may be found on the last page.

FEATURES

HIGHLIGHTS

- Single chip PLL:

- Features

0.5 m Hz to 560 Hz bandwidth

- Provides node clock for ITU-T G.8261/G.8262 Synchronous Ethernet (Sync E)

- Exceeds GR-253-CORE (OC-192) and ITU-T G.813 (STM-64) jitter generation requirements

- Provides node clocks for Cellular and WLL base-station (GSM and 3G networks)

- Provides clocks for DSL access concentrators (DSLAM), especially for Japan TCM-ISDN network timing based ADSL equipments

- Provides clocks for 1 Gigabit and 10 Gigabit Ethernet applications

- It supports clock generation for IEEE-1588 application

MAIN FEATURES

- Provides an integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 3, 4E, 4, SMC, EEC-Option 1 and EEC-Option 2 Clocks

- Provides SONET clocks with less than 1 ps of RMS Phase Jitter (12 k Hz

- 20 MHz)

- Supports 1PPS input and output

- Employs PLL architecture to...