83026I-01 Overview

Description

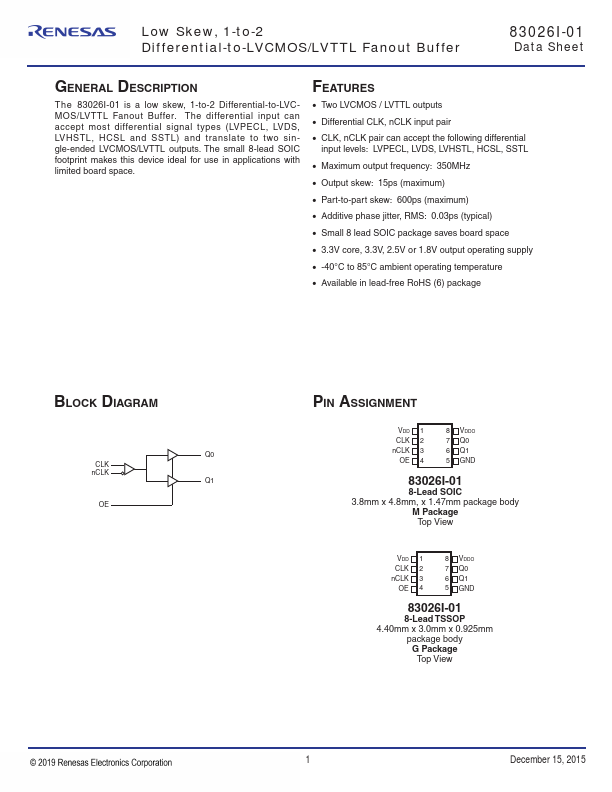

The 83026I-01 is a low skew, 1-to-2 Differential-to-LVCMOS/LVTTL Fanout Buffer. The differential input can accept most differential signal types (LVPECL, LVDS, LVHSTL, HCSL and SSTL) and translate to two single-ended LVCMOS/LVTTL outputs.

Key Features

- Two LVCMOS / LVTTL outputs

- Differential CLK, nCLK input pair

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 350MHz

- Output skew: 15ps (maximum)

- Part-to-part skew: 600ps (maximum)

- Additive phase jitter, RMS: 0.03ps (typical)

- Small 8 lead SOIC package saves board space

- 3.3V core, 3.3V, 2.5V or 1.8V output operating supply

- 40°C to 85°C ambient operating temperature