843S06

843S06 is PLL Clock Synthesizer manufactured by Renesas.

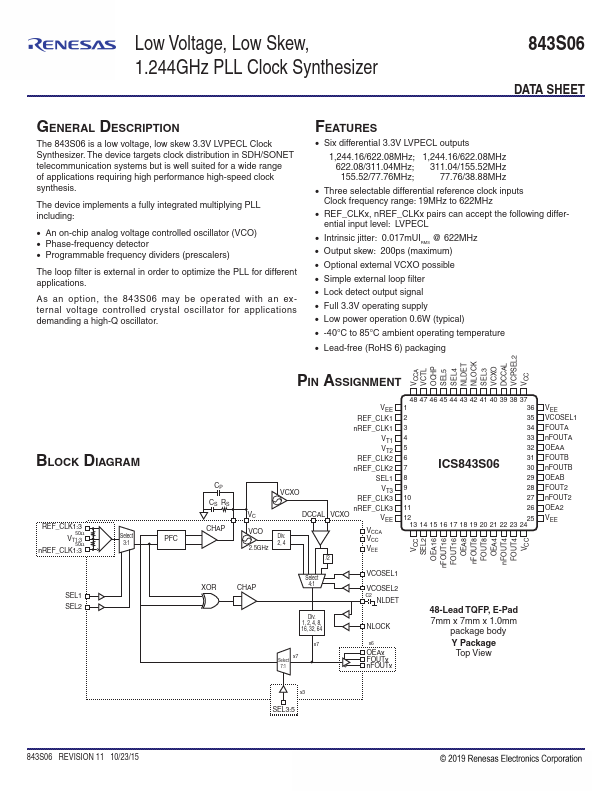

Low Voltage, Low Skew, 1.244GHz PLL Clock Synthesizer

DATA SHEET

GENERAL DESCRIPTION

The 843S06 is a low voltage, low skew 3.3V LVPECL Clock Synthesizer. The device targets clock distribution in SDH/SONET telemunication systems but is well suited for a wide range of applications requiring high performance high-speed clock synthesis.

The device implements a fully integrated multiplying PLL including:

- An on-chip analog voltage controlled oscillator (VCO)

- Phase-frequency detector

- Programmable frequency dividers (prescalers)

The loop filter is external in order to optimize the PLL for different applications.

As an option, the 843S06 may be operated with an external voltage...