854S006

Description

The 854S006 is a low skew, high performance 1-to-6, Differential-to-LVDS fanout buffer. The CLK, n CLK pair can accept most standard differential input levels. The 854S006 is characterized to operate from either a 2.5V or a 3.3V power supply. Guaranteed output and part-to-part skew characteristics make the 854S006 ideal for those clock distribution applications demanding well defined performance and repeatability.

Features

- Six differential LVDS outputs

- One differential clock input pair

- CLK, n CLK pair can accept the following differential input levels: LVDS, LVPECL, LVHSTL, SSTL, HCSL

- Maximum output frequency: 1.7GHz

- Translates any single-ended input signal to LVDS levels with resistor bias on n CLK input

- Output Skew: 55ps (maximum)

- Propagation delay: 850ps (maximum)

- Additive phase jitter, RMS: 0.067ps (typical)

- Full 3.3V or 2.5V supply

- -40°C to 85°C ambient operating temperature

- Available in lead-free (Ro HS 6) package

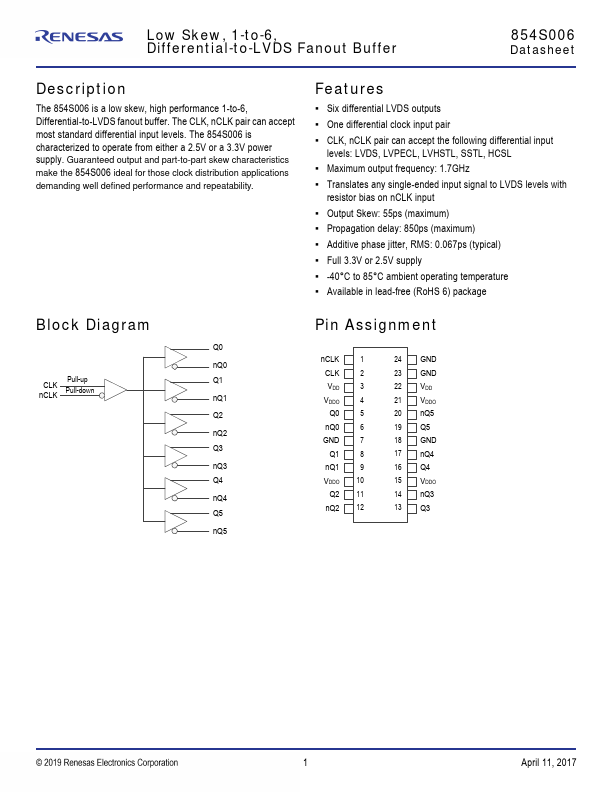

Block Diagram

Q0 n Q0

CLK n...