89HPES32H8 Overview

Key Specifications

Package: FCBGA

Mount Type: Surface Mount

Pins: 900

Operating Voltage: 1 V

Key Features

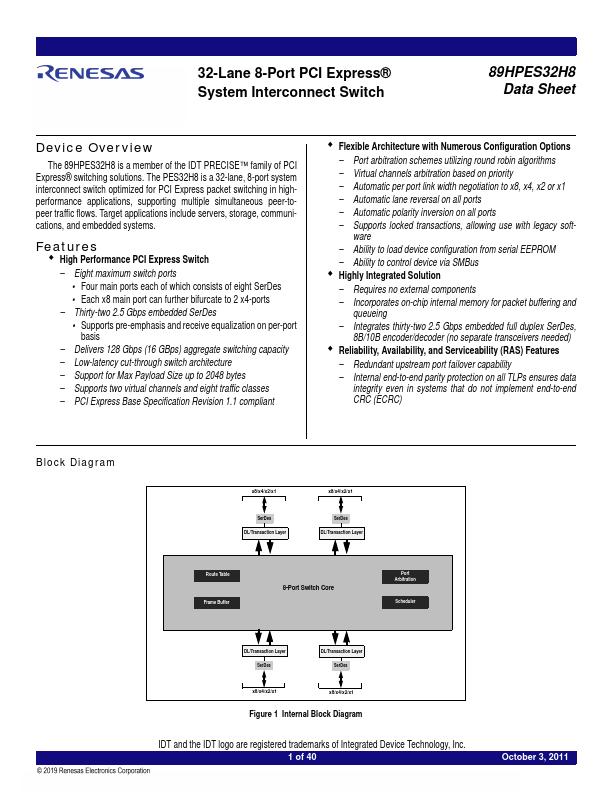

- High Performance PCI Express Switch – Eight maximum switch ports

- Four main ports each of which consists of eight SerDes

- Each x8 main port can further bifurcate to 2 x4-ports – Thirty-two 2.5 Gbps embedded SerDes