8P73S674

Description

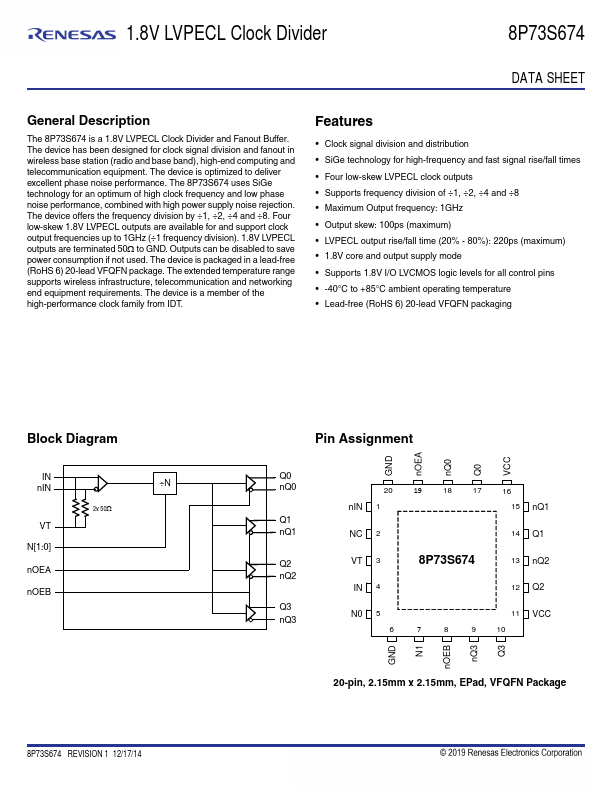

The 8P73S674 is a 1.8V LVPECL Clock Divider and Fanout Buffer.

Key Features

- Clock signal division and distribution

- SiGe technology for high-frequency and fast signal rise/fall times

- Four low-skew LVPECL clock outputs

- Maximum Output frequency: 1GHz

- Output skew: 100ps (maximum)

- LVPECL output rise/fall time (20% - 80%): 220ps (maximum)

- 1.8V core and output supply mode

- Supports 1.8V I/O LVCMOS logic levels for all control pins

- 40°C to +85°C ambient operating temperature

- Lead-free (RoHS 6) 20-lead VFQFN packaging