8SLVP1208

8SLVP1208 is LVPECL Output Fanout Buffer manufactured by Renesas.

Description

The 8SLVP1208 is a high-performance differential LVPECL fanout buffer. The device is designed for the fanout of high-frequency, very low additive phase-noise clock and data signals. The 8SLVP1208 is characterized to operate from a 3.3V and 2.5V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8SLVP1208 ideal for those clock distribution applications demanding well-defined performance and repeatability. Two selectable differential inputs and eight low skew outputs are available. The integrated bias voltage generators enables easy interfacing of single-ended signals to the device inputs. The device is optimized for low power consumption and low additive phase noise.

Features

- Eight low skew, low additive jitter LVPECL output pairs

- Two selectable, differential clock input pairs

- Differential pairs can accept the following differential input levels: LVDS, LVPECL, CML

- Maximum input clock frequency: 2GHz

- LVCMOS interface levels for the control input (input select)

- Output skew: 28ps (typical)

- Propagation delay: 410ps (maximum)

- Low additive phase jitter, RMS: 54.1fs (maximum)

(f REF = 156.25MHz, VPP = 1V, 12k Hz- 20MHz)

- Full 3.3V and 2.5V supply voltage

- Maximum device current consumption (IEE): 141m A

- Available in lead-free (Ro HS 6), 28-Lead VFQFPN package

- -40°C to 85°C ambient operating temperature

- Supports case temperature ≤ 105°C operations

- Differential PCLK0, n PCLK0 and PCLK1, n PCLK1 pairs can also accept single-ended LVCMOS levels. See Applications section Wiring the Differential Input to Accept Single-Ended Levels (Figure 1A and Figure 1B)

- Supports PCI Express Gen1- 5

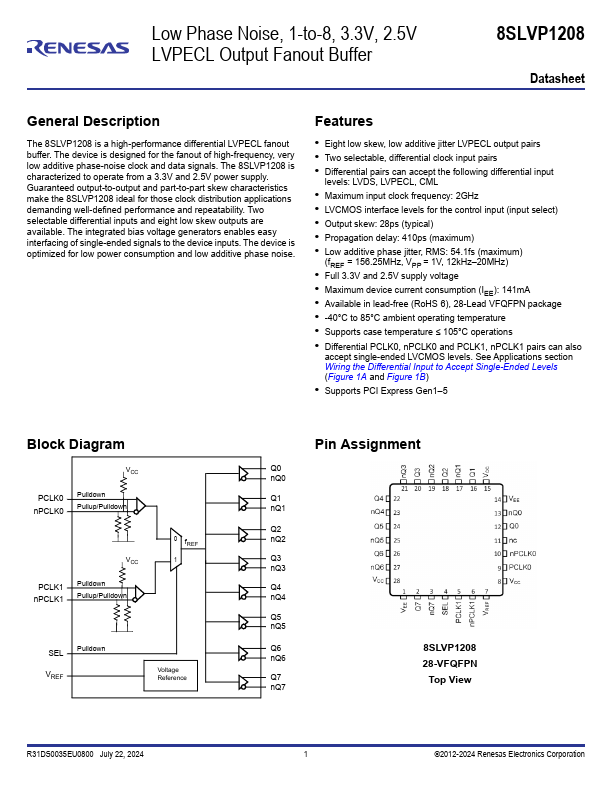

Block Diagram

PCLK0 n PCLK0

Pulldown Pullup/Pulldown

PCLK1 n PCLK1

Pulldown Pullup/Pulldown

0 f REF 1

SEL Pulldown VREF

Voltage Reference

Pin Assignment

Q0 n Q0

Q1 n Q1

Q2 n Q2

Q3 n Q3

Q4 n Q4

Q5 n Q5

Q6

8SLVP1208 n Q6

28-VFQFPN

Q7...