9DB306 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 28

Operating Voltage: 3.3 V

Description

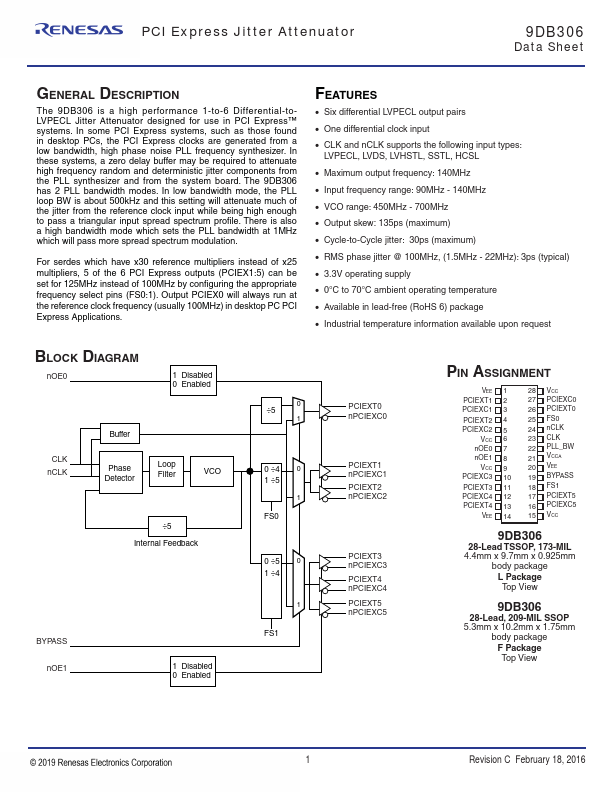

The 9DB306 is a high performance 1-to-6 Differential-toLVPECL Jitter Attenuator designed for use in PCI Express™ systems. In some PCI Express systems, such as those found in desktop PCs, the PCI Express clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer.

Key Features

- Six differential LVPECL output pairs

- One differential clock input

- CLK and nCLK supports the following input types: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Maximum output frequency: 140MHz

- Input frequency range: 90MHz

- VCO range: 450MHz

- Output skew: 135ps (maximum)

- Cycle-to-Cycle jitter: 30ps (maximum)

- RMS phase jitter @ 100MHz, (1.5MHz

- 22MHz): 3ps (typical)