| Part | 9DBL0252C |

|---|---|

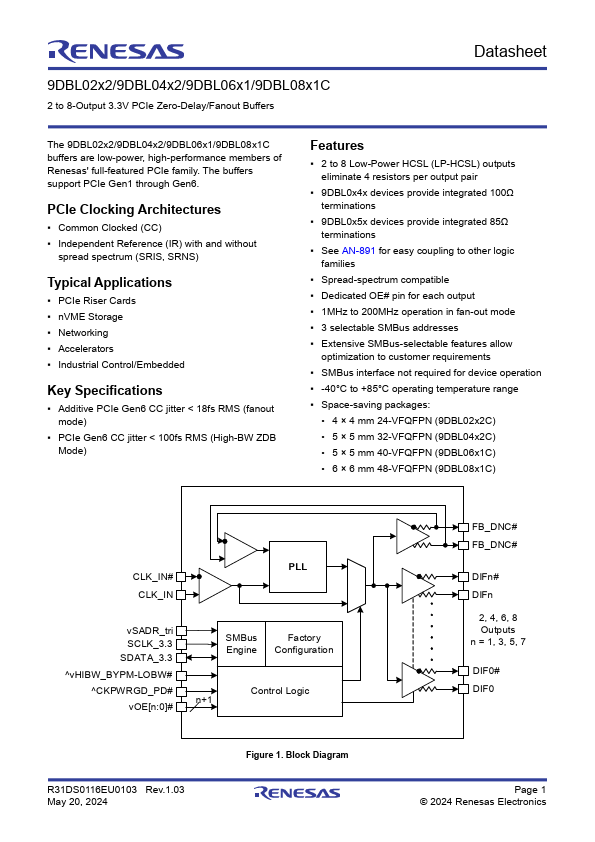

| Description | 2 to 8-Output 3.3V PCIe Zero-Delay/Fanout Buffers |

| Manufacturer | Renesas |

| Size | 1.39 MB |

Pricing from 3 USD, available from DigiKey and Avnet.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 0 | 1+ : 3 USD 10+ : 2.249 USD 25+ : 2.0596 USD 100+ : 1.8518 USD |

View Offer |

| DigiKey | 0 | 1+ : 3 USD 10+ : 2.249 USD 25+ : 2.0596 USD 100+ : 1.8518 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 9DBL0252 | IDT | 2-output 3.3V PCIe Zero-Delay Buffer |

| 9DBL0255 | IDT | PCIe Gen1-5 Clock Fanout Buffers |

| 9DBL0253 | IDT | 2-Output 3.3V LP-HCSL Zero-Delay Buffer |